General Assembly of European Processor Initiative has selected a new Chairman of the Board in July. Eric Monchalin from Atos, the company that coordinates the EPI project, is going to lead 28 partners from 10 countries in their efforts to design and implement a roadmap for a new family of low-power European processors.

Eric is experienced in leading 100+ people organizations and managing multi tens millions of Euros projects in international environments. He is a technology-minded person who values wide range of skills and technological knowledge focused on customer expectations to turn them into reality. Furthermore, Eric’s career has been mainly built on numerous Hardware and Software R&D positions in several companies and various domains like signal processing, embedded systems, communication, storage, High Performance Computing and Artificial Intelligence.

The European Processor Initiative, a project with 27 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC technologies, is finishing its second year of activities.

Despite 2020 bringing upon our young efforts the circumstances that were previously unimaginable, causing the subsequent cancellation of the first-ever planned European Processor Initiative Forum, the partners in the Initiative managed to stay the course and maintain all activities in all designated streams.

The year began with our latest partner, SiPearl, launching to start their activities dedicated to developing commercialized implementations of our technology. Very soon after announcing their presence on the global stage, SiPearl signed a licensing agreement with Arm and opened a branch in Germany.

At the same time, European Processor Initiative partners have finalized the first version of our RISC-V accelerator architecture, named EPAC, and we look forward to the delivery of the first European Processor Initiative silicon featuring EPAC Test Chip in the exciting year that follows. The EPAC Test Chip silicon will be complemented with PCIe EPAC Test Platform enabling the test and enhancements of the architecture for future revisions.

At the software level, we already have a compiler supporting RISC-V vector intrinsics and automatic parallelization of C/C++ codes. We are evaluating the generated code on emulation platforms that provide detailed insight for the holistic co-design of applications, compiler, and architecture. We also have other software development vehicles (SDV) where we are adapting the Operating System for the Heterogeneous ARM+RISC-V architecture of the European Processor Initiative project.

Our automotive activities in the previous year have been focused on the design of state-of-the-art automotive high-performance computing proof-of-concept with the ambition to demonstrate how European Processor Initiative IP will enable future ADAS functionality, paving the way to exploit the GPP, the RISC-V platform, the Kalray MPPA, and the Menta eFPGA IP.

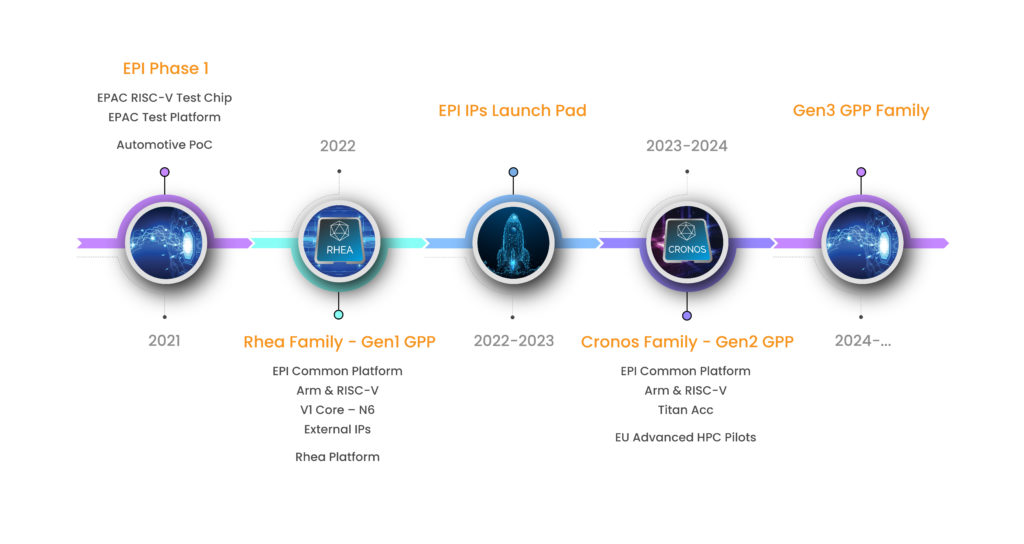

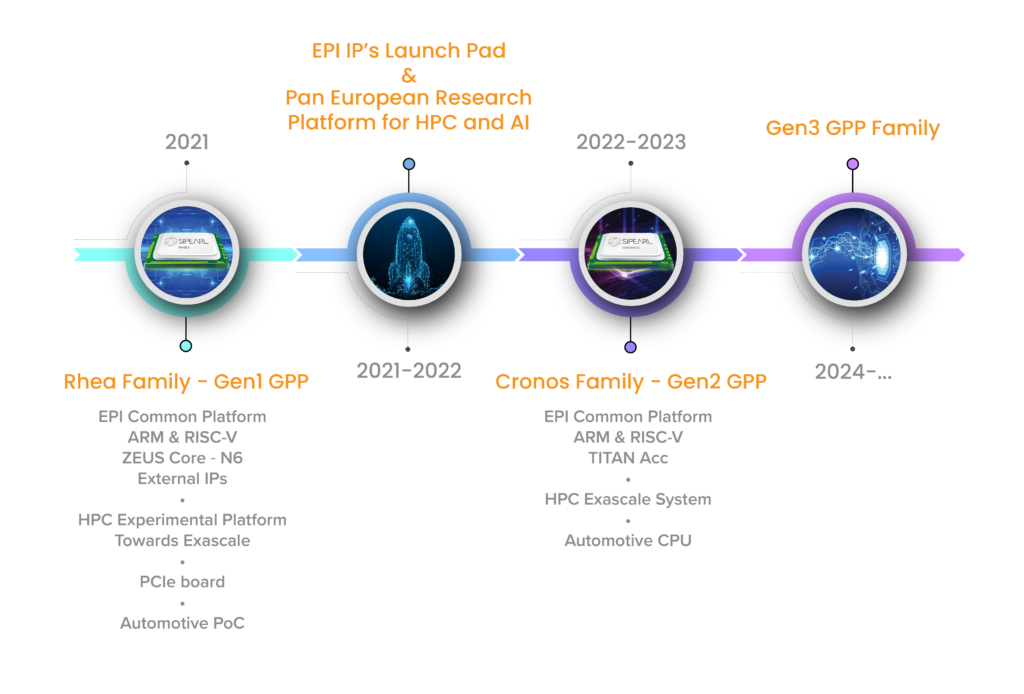

Based on this project progress, the Consortium is ready to announce the updated project roadmap shown below:

European Processor Initiative will, together with colleagues from other European exascale projects, attend the virtual Supercomputing20, where we will showcase our latest developments and update to the roadmap. We invite you to attend our virtual booth and join in the lively discussions about the future of HPC!

The project is finishing its first year with introduction of a new EPI Common Platform, an updated roadmap and presence at key events

The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 27 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC technologies, is approaching the closure of the first year in its three-year cycle.

During that time, the consortium has submitted several architectural designs to the European Commission and is now ready to show its updated roadmap to the public.

Figure 1. EPI Roadmap

The first-generation chip family, named Rhea, will include Arm ZEUS architecture general purpose cores and prototypes of high energy-efficient accelerator tiles: RISC-V based (EPAC), Multi-Purpose Processing Array (MPPA), embedded FPGA (eFPGA) and cryptography HW engine. First Rhea chips will be fabricated in N6 technology aiming at the highest processing capabilities and energy efficiency.

The Rhea chips will be integrated into test platforms, both in workstations and supercomputers in order to validate the hardware units, develop the necessary software interfaces, and run applications. Rhea aims to be the European processor for several experimental platforms towards exascale HPC and future automotive designs.

Today we also announce our long-term commitment to our recently introduced initiative to harmonize the heterogeneous computing environment by defining a common approach: the EPI Common Platform (CP). The EPI CP is in early development but will include the global architecture specification (hardware and software), common design methodology, and global approach for power management and security, in the future.

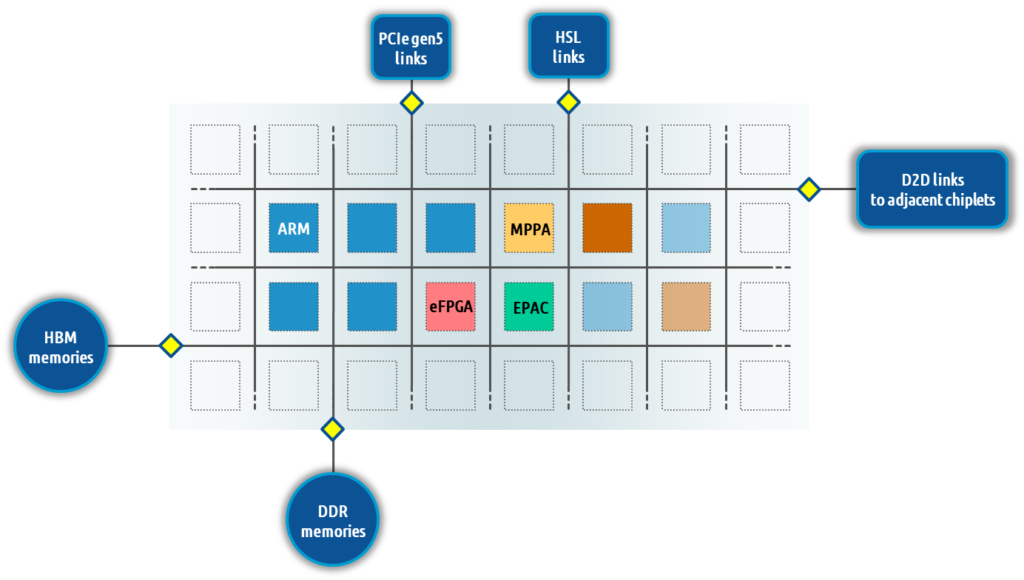

The CP in the Rhea family of processors will be organized around a 2D-mesh Network-on-Chip (NoC) connecting computing tiles based on general purpose Arm cores with previously mentioned accelerator tiles.

Figure 2. EPI Common Platform

A common software environment between heterogeneous computing tiles will harmonize the system, acting as a common backbone of IP components for IO connection with the external environment such as memories and interconnected or loosely coupled accelerators.

With this CP approach, EPI will provide an environment that can seamlessly integrate any computing tile. The right balance of computing resources matching the application needs will be defined through the carefully designed ratio of the accelerator and general-purpose tiles.

These important developments and more will all be presented at high-profile events the Initiative is attending, announced on EPI’s web: https://www.european-processor-initiative.eu/events/.

We invite all interested parties to visit our exhibition booths at upcoming events, with special focus on the Supercomputing Conference in Denver, USA (Nov 17-22, 2019), booth #895, and the European Forum for Electronic Components and Systems in Helsinki, Finland (Nov 19-21, 2019).

Meet us there to discuss EPI’s future!

Last week has been loaded with activities for the European Processor Initiative. Our team attended several very important events, where EPI was discussed and our road to the low-power processor presented.

EPI Chairman of the Board, Jean-Marc Denis, attended two events, in a Transatlantic hop, skip and a jump: first, the 73rd HPC User Forum in Chicago, where he presented EPI’s objectives and its interlink with the European Union’s EuroHPC Joint Undertaking, only to go back to Parallel Computing conference in Prague, with a similar mission. His talk concluded in presenting EPI’s challenges for the upcoming period: building on existing IP and communities and closing the gap between research and innovation and industrial products.

At the same time, beautiful cities of Bologna and Pisa hosted two events where the Initiative presented its objectives and roadmap.

In Bologna, at the Italian Workshop on Parallel and High-Performance Computing Technologies, the European Processor Initiative presented the EPI project to the Italian HPC academia and to the industrial users.

The academic participants presented their research lines and their previous engagement and contributions to EU programs, covering a wide spectrum of research fields and technological implementation. Andrea Bartolini (UniBO) presented the goals of the EPI, the members of the consortium and the roadmap for the processor, the accelerator and the automotive components, and highlighted the role of University of Bologna in the development of key components of the EPI project. Fabrizio Magugliani (E4 computer Engineering) presented the role of E4 in the development of key components of the EPI projects such as the PCIe daughter board hosting the EPI processor as Software Development Vehicle. The presentation opened a healthy discussion about how the community of Italian researchers could leverage the EPI project bringing the results of their research and therefore adding value to the project.

In Pisa, the EPI team participated at the RoundTable at ApplePies, 7th International Workshop Applications in Electronics Pervading Industry, Environment & Society. The Round Table confirmed that the EuroHPC Joint Undertaking, in full alignment with the objective of deploying in Europe a world-class supercomputing infrastructure and a competitive innovation ecosystem in supercomputing technologies, applications and skills by coordinating the efforts of its member states and share resources, has assigned one of the 3 Precursor to Exascale system to CINECA. Building on that, the Round Table’s participants presented the contribution of Italian-based institutions and enterprises towards the maximization of the results achieved through exascale-class systems both from the scientific and research point of view as well as from the industrial point of view. The current status of R&D in Italy specifically for the development of components for exascale-class systems was addressed, including the role of Italian institutions and enterprises in the European Processor Initiative (EPI) consortium, and which synergies among the key players could create a native Italian ecosystem fully aligned within the EuroHPC JU and EPI initiatives for enabling exascale-class systems to support scientific leadership and industrial competitiveness.

The week was finished by Atos team members participating at the Arm Research Summit in Texas, USA. Romain Dolbeau and Ying-Chih Yang gave a talk at the workshop “Impact of Arm hardware from an HPC application perspective (present and future-looking)”. The key objective of the workshop was gathering expertise from various research groups (runtime systems, linear algebra, operating system, performance modeling,…) to discuss key features and shape next-generation applications.