General Assembly of European Processor Initiative has selected a new Chairman of the Board in July. Eric Monchalin from Atos, the company that coordinates the EPI project, is going to lead 28 partners from 10 countries in their efforts to design and implement a roadmap for a new family of low-power European processors.

Eric is experienced in leading 100+ people organizations and managing multi tens millions of Euros projects in international environments. He is a technology-minded person who values wide range of skills and technological knowledge focused on customer expectations to turn them into reality. Furthermore, Eric’s career has been mainly built on numerous Hardware and Software R&D positions in several companies and various domains like signal processing, embedded systems, communication, storage, High Performance Computing and Artificial Intelligence.

SiPearl, EPI’s industrial and business hand, joins the EPI consortium as its 27th partner and moves into its operational phase.

SiPearl and its solutions will help drive the development of the European market for high-performance computing (HPC), as well as its strategic applications such as artificial

intelligence and connected mobility. SiPearl will develop and market its solutions through close collaboration with its 26 partners from the EPI – scientific community, supercomputing centers and leading names from the IT, electronics and automotive sectors – which are its stakeholders and future clients.

Read the full press release here: https://www.sipearl.com/press/PR_SiPearl_launching_21012020.pdf and visit the company website here: https://www.sipearl.com/.

The project is finishing its first year with introduction of a new EPI Common Platform, an updated roadmap and presence at key events

The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 27 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC technologies, is approaching the closure of the first year in its three-year cycle.

During that time, the consortium has submitted several architectural designs to the European Commission and is now ready to show its updated roadmap to the public.

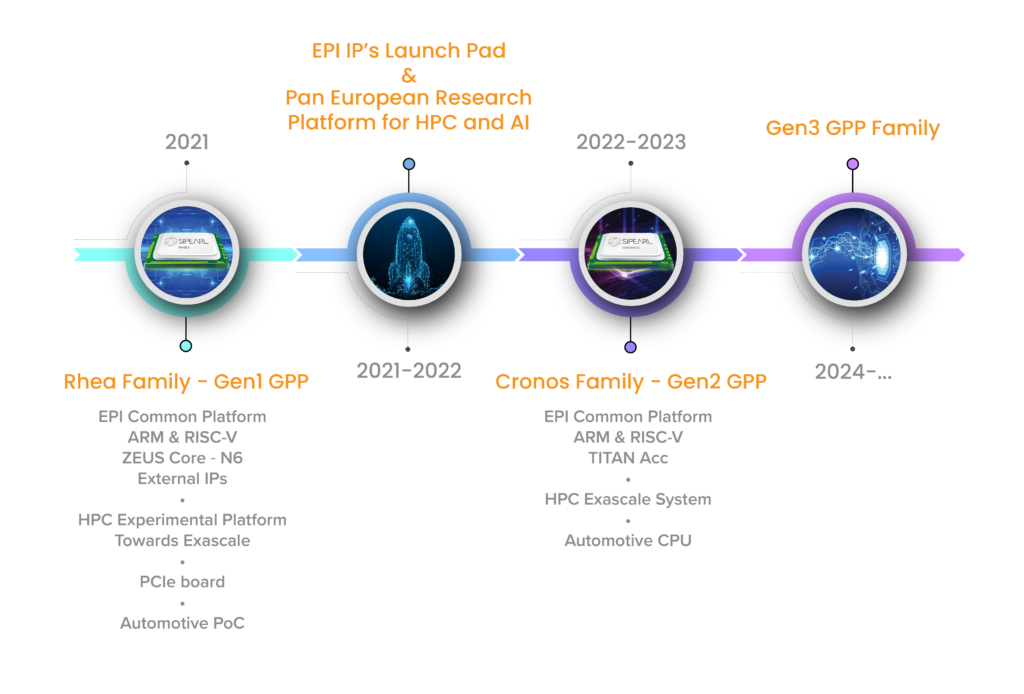

Figure 1. EPI Roadmap

The first-generation chip family, named Rhea, will include Arm ZEUS architecture general purpose cores and prototypes of high energy-efficient accelerator tiles: RISC-V based (EPAC), Multi-Purpose Processing Array (MPPA), embedded FPGA (eFPGA) and cryptography HW engine. First Rhea chips will be fabricated in N6 technology aiming at the highest processing capabilities and energy efficiency.

The Rhea chips will be integrated into test platforms, both in workstations and supercomputers in order to validate the hardware units, develop the necessary software interfaces, and run applications. Rhea aims to be the European processor for several experimental platforms towards exascale HPC and future automotive designs.

Today we also announce our long-term commitment to our recently introduced initiative to harmonize the heterogeneous computing environment by defining a common approach: the EPI Common Platform (CP). The EPI CP is in early development but will include the global architecture specification (hardware and software), common design methodology, and global approach for power management and security, in the future.

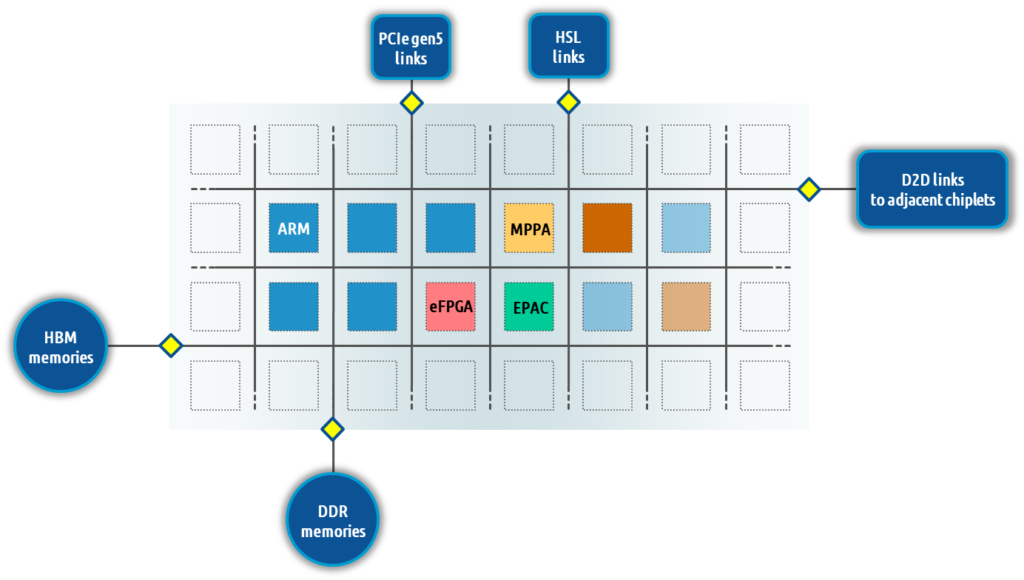

The CP in the Rhea family of processors will be organized around a 2D-mesh Network-on-Chip (NoC) connecting computing tiles based on general purpose Arm cores with previously mentioned accelerator tiles.

Figure 2. EPI Common Platform

A common software environment between heterogeneous computing tiles will harmonize the system, acting as a common backbone of IP components for IO connection with the external environment such as memories and interconnected or loosely coupled accelerators.

With this CP approach, EPI will provide an environment that can seamlessly integrate any computing tile. The right balance of computing resources matching the application needs will be defined through the carefully designed ratio of the accelerator and general-purpose tiles.

These important developments and more will all be presented at high-profile events the Initiative is attending, announced on EPI’s web: https://www.european-processor-initiative.eu/events/.

We invite all interested parties to visit our exhibition booths at upcoming events, with special focus on the Supercomputing Conference in Denver, USA (Nov 17-22, 2019), booth #895, and the European Forum for Electronic Components and Systems in Helsinki, Finland (Nov 19-21, 2019).

Meet us there to discuss EPI’s future!

Impressions from the EuroHPC Summit Week 2019, that was held from 13 to 17 May in Poznań, Poland, are still fresh, as the event turned out a huge number of attendees and interesting topics covered in the 4-day event.

European Processing Initiative, under the moderating lead of Mr Leonardo Flores Añover and Mr Andrea Feltrin from DG CNECT, participated in a half-day workshop titled “Co‐designing with the European Processor Initiative”. The goals of the workshop were to identify applications that could drive co‐design for EPI and the pilot system projects; introduce attendees to co‐design for EPI and pilot system ideas leading to supercomputers based on EPI technologies; discuss component‐level vs. system‐level co‐design: who does what when; highlight ongoing co‐design efforts within EPI; bring application and technology/system architecture experts together; show the current status of the software landscape, and discuss how they can contribute to a coherent effort towards the European Exascale supercomputers.

Presenters from EPI covered those topics in 6 short presentations, while the session closed with an expert panel. Participants of the panel emphasized the importance of selecting a set of communities and involving them strongly in the co-design process. The communities should be those that really need Exascale performance, have high societal impact and are committed to participate in the co-design work. The systems in question will be heterogeneous and it is important to make them as user-friendly as possible; therefore, the middleware and programming environment play a very important role.

The panel also concluded that the use of HPC systems as workflows is increasing – they very often contain HPC with HPDA and AI. At Exascale level, workflows add an order of magnitude to the complexity. Using the sole general purpose processor combined at interposer level with many different accelerators helps drive the complexity down. EPI offers this unique feature. It is very important to provide middleware to properly support for workflows, also on heterogeneous systems.

The pilot system must demonstrate scalability, energy efficiency and reliability. Risks should be limited to a particular aspect/component of the system and the pilots should be operational, enable application running on them to prepare for Exascale, and provide results that increase visibility. The panel believes such visibility can be ensured through training as well – it is an opportunity to attract more people to the HPC field. It should be more attractive for young people, starting as early as school level. The panel concluded, looking to the future developments, that after Exascale, the goal should be not so much related to increasing speed, but making the Exascale systems much more efficient. Real-world application and workflow efficiency, as well as performance, need to be increased.

Jean-Marc Denis, Chairman of the Board of the European Processor Initiative, attended the Supercomputing Asia event in Singapore, at the Suntec Singapore Convention and Exhibition Centre, presenting EPI activities and efforts.

Visitors to SC Asia could also find out more about EPI’s goals and roadmap by visiting the European Commission booth, which graciously hosted EPI materials, flyers and posters. Pictured here is Sébastien Varrette, from the Université du Luxembourg, at the EC/EPI/PRACE booth.