# **CLOUD CONTINUUM & SWARM COMPUTING**

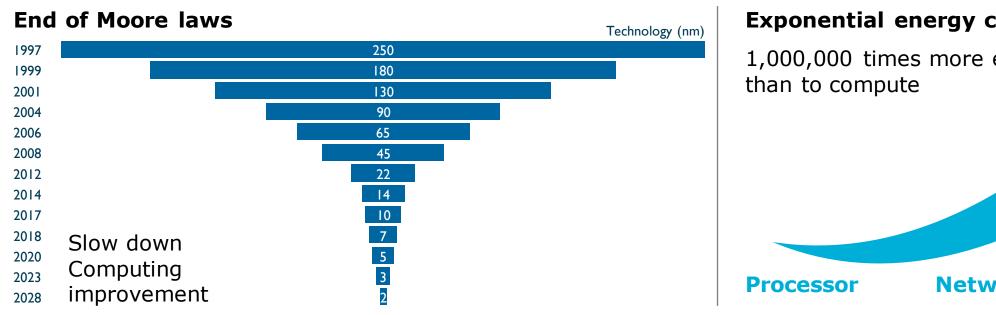

#### THE REALITY HAS TO FIT TECHNOLOGIES CAPABILITIES

# **Exponential energy cost to move data** 1,000,000 times more energy to store

**Network Storage**

#### Capabilities to move and store data are diverging

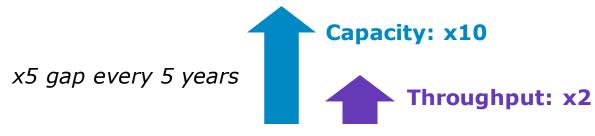

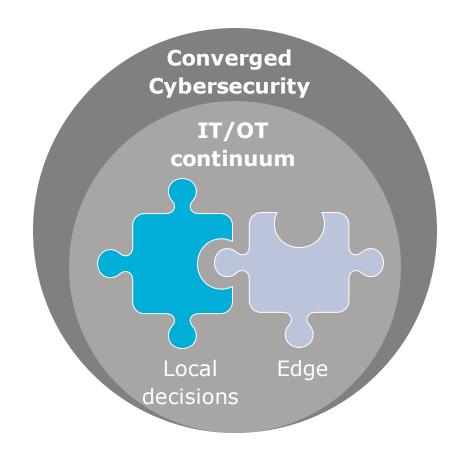

## THE RAISE OF COOPERATION AT THE EDGE

#### **Vertical hierarchy to transversal cooperation**

## FROM ANIMAL SWARMS TO MAN MADE SWARMS

**Animal swarms**

Inspired by Nature

**Customer Service Avatars**

**Industry 4.0**

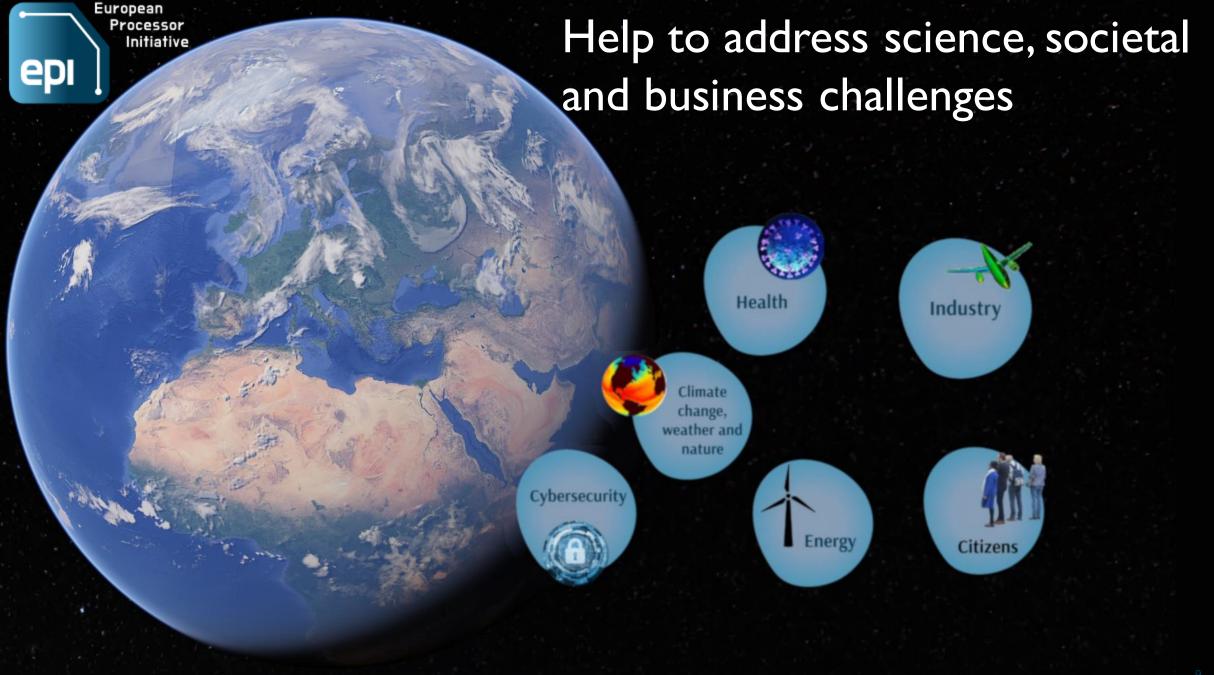

## **EUROPEAN PROCESSOR INITIATIVE**

## THE EU HPC TIMELINE

EPI 1

EPI 2

2017

2018

2019

2020

2021

2022

2023

2024

Mar 2017

EC launched the *EuroHPC* declaration

Nov 2018 EuroHPC JU

#### Sept 2020.

v. d. Leyen: State of the Union

- NextGenerationEU

- Europe's digital sovereignty

- investment of 8 billion euros in the next generation of supercomputers

- European industry to develop our own next-generation microprocessor

**Sept 2021.**

v. d. Leyen: State of the Union

new European Chips Act

T.Breton

supercomputing is at the forefront of our digital sovereignty, encompassing industrial, technological and scientific challenges

Jul 2021. EU Council

established new EuroHPC JU

Serve EuroHPC objectives:

Building a leading European HPC ecosystem

✓ Contribute to the development of European supercomputing technologies that can compete on the global HPC market.

✓ Key ingredient of the EU to equip itself with a world-class supercomputing infrastructure.

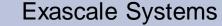

## THE ECOSYSTEM ROAD TO EU EXASCALE

SGA1:

GPP & Accelerator test chips

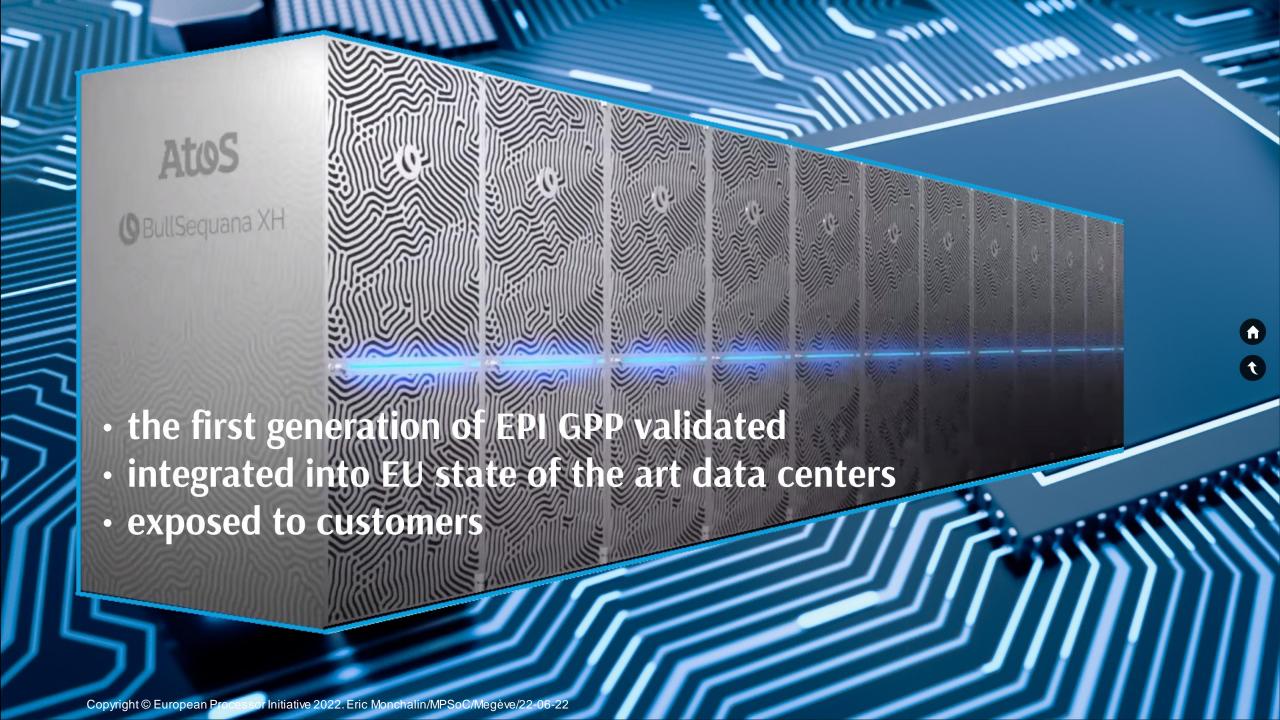

GPP V1 Go to Market

Accelerator Demonstrator

Next project(s)

GPP V2 Go to Market

Accelerator V1 Go to Market

Centres of Excellence in HPC Applications

2019 – 2021 2022 - 2024 2025 -

#### **EPI PROJECT FACTSHEET**

- Phase 1 successfully concluded (2019-2021)

- **Currently in Phase 2 (2022-2024)**

- Consortium of 30 European academic and industrial partners from 11 countries

- Funded by EuroHPC JU (50%) and co-funded by Croatia, France, Germany, Greece, Italy, the Netherlands, Portugal, Spain, Sweden and **Switzerland**

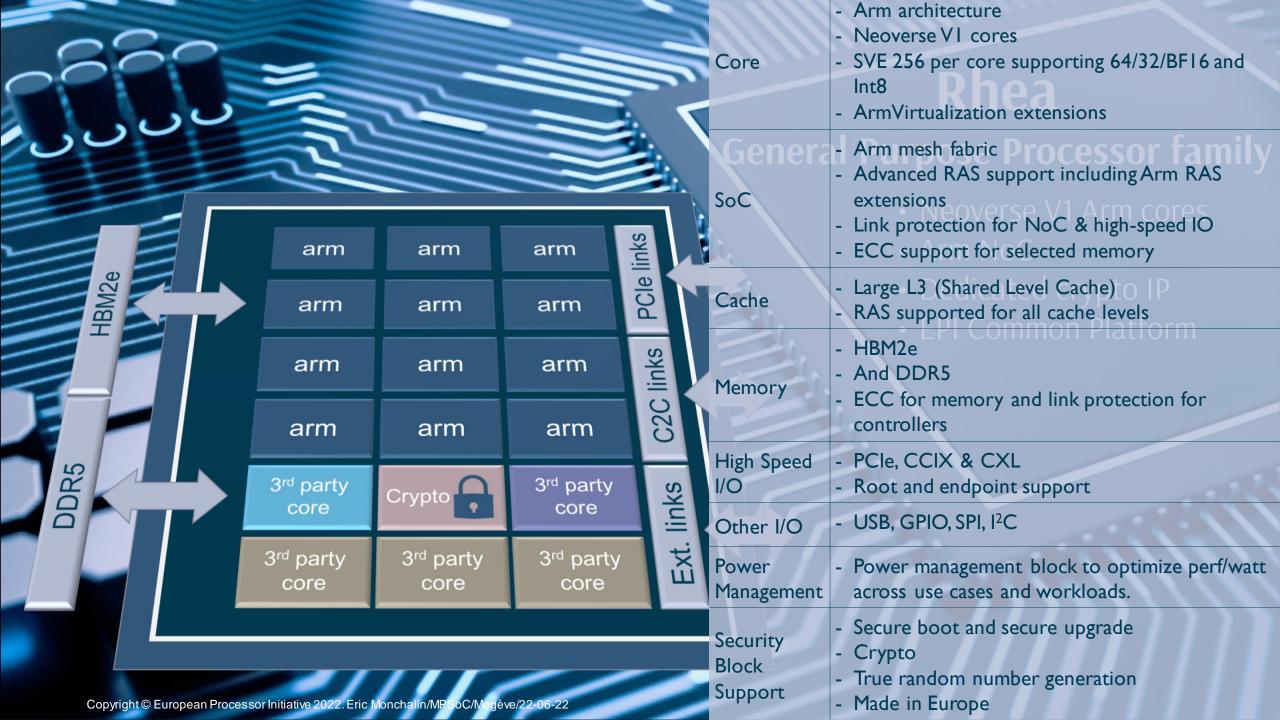

#### Rhea Family - Gen1 GPP

## **EPI2 TIMELINE**

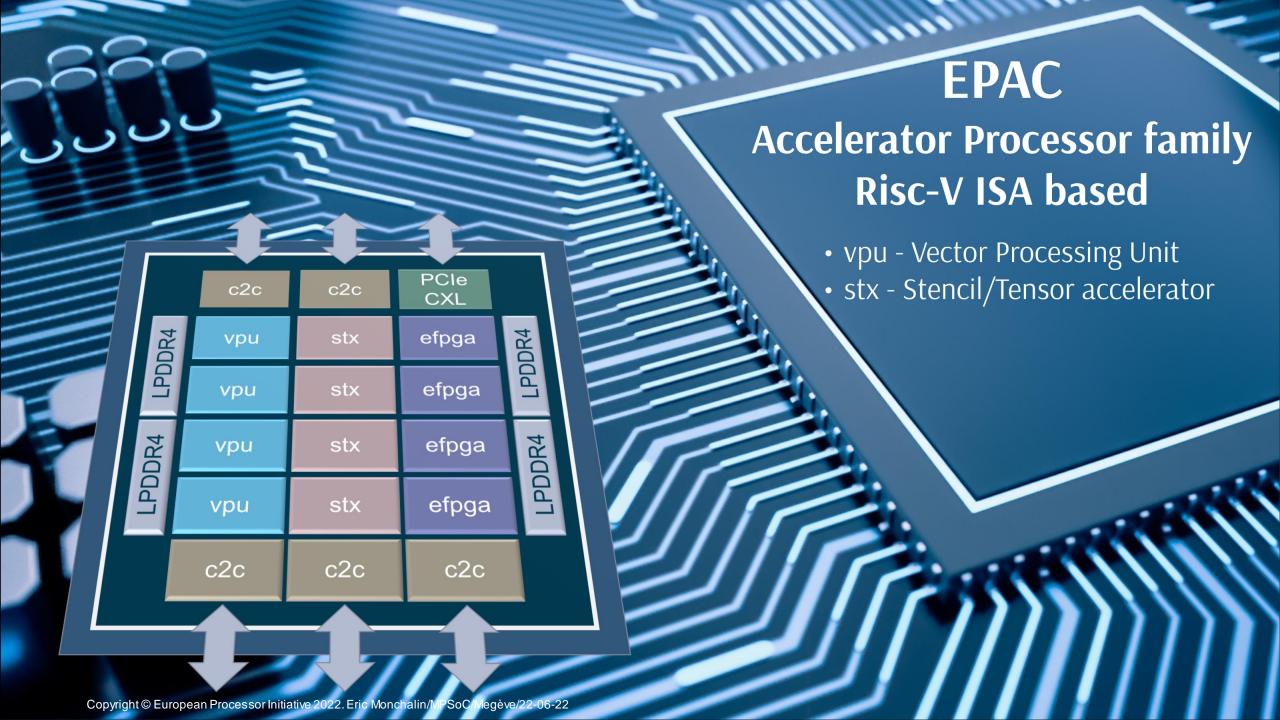

**EPI Common Platform** Arm & Risc-V (STX, VRP, ..) Arm Neoverse V1 Core - N6 External IP's

EPAC V1.5 multi-node demonstration cluster

EPAC V2.0 sent for manufacturing

Cronos Family - Gen3 GPP

EU Exascale system with Rhea2 processors

Hurricane PCIe Acceleration card based on EPAC technology

Dual chiplet implementation First EU Exascale system with Rhea processors FPGA Die-to-Die Demonstrator of the HW Common Platform

RISC-V KVX FPGA emulator

**EPAC V2.0 Platform**

KVX RISC-V based accelerator architecture definition

> Menta FPGA chiplet architecture definition

#### **Must have Must Have Must have** Open/Standard Open/Standard On-permise & in Rhea **HW** interfaces SW interfaces (UCle, CXL, PCle) (UCle, CXL, PCle) General Purpose Processor family **CPU** Core count is CPUs still matter. GPUs growing (fast). and ACCs don't fit all needs What's the trade-off? • Neoverse V1 Arm cores Arm NoC Dedicated crypto IP arm xPU: (toward) a unified CPU: No time spent on optimization programming model • EPI Common Platform Must Have Must Have Global and unified memory arm Bytes/Flops MEM bound → CPUs Max mem BW → HBM **HBM** Power efficiency Slow memory only when (perf on <u>real</u> apps per watt) required really matters $\rightarrow$ DDR → HPCG Copyright © European Processor Initiative 2022. Enc initiatini viral ochwege verzz-00-22

- Help EU digital sovereignty

- Seed an EU high-end processor industry (Arm & Risc-V based)

- Contribution to a Risc-V open ecosystem

- Address HPC and Big-Data markets.

- One of the foundations of the new EU Chips Act

European Processor Initiative is a cornerstone of EU digital agenda and EU digital sovereignty

## **THANK YOU**

- www.european-processor-initiative.eu

- @EuProcessor

- in European Processor Initiative

- European Processor Initiative