# THE EUROPEAN APPROACH FOR EXASCALE AGES

HOW DOES THE FUTURE PROCESSORS LOOK LIKE?

Jean-marc.denis@European-processor-initiative.eu

Chairman of the Board

THIS PROJECT HAS RECEIVED FUNDING FROM THE EUROPEAN UNION'S HORIZON 2020 RESEARCH AND INNOVATION PROGRAM UNDER GRANT AGREEMENT NO 826647

#### CONTEXT

# **European Commission President Jean-Claude Juncker**

Paris, 27 October 2015

« Our ambition is for Europe to become one of the top 3 world leaders in high-performance computing by 2020 »

# **Creation of the European processor Initiative**

23 members from 10 EU countries

- → General Purpose processor in 2022

- Accelerator IP

Brussels, 1 Dec 2017

#### Vice President Andrus Ansip

« I encourage even more EU countries to engage in this ambitious endeavour »

Digital Day Rome, 23 March 2017

Ministers from seven MS (France, Germany, Italy, Luxembourg, Netherlands, Portugal and Spain) sign a declaration to support the next generation of computing and data infrastructures

### Ursula Von Der Lyen State of the Union

Brussels – September, 16th, 2020

- Investment of 8 billion euros in the next generation of supercomputers - cuttingedge technology made in Europe.

- The European industry will develop our own next-generation microprocessor

#### **EPI OBJECTIVES**

- Overall: Develop a complete EU designed high-end microprocessor, addressing Supercomputing and edge-HPC segments

- Short-term objective

- supply the EU-designed microprocessor to empower the EU Exascale machines

- Long-term objective

- Europe needs a sovereign (=not at risk of limitation or embargo by non-EU countries) access to high-performance, low-power microprocessors, from IP to products

- EPI has been set to fulfil this objective

- EPI has to cover all Technical Readiness levels (TRL)

- TRL 1-3 are for long-term objectives (EU IP)

\*and\*

TRL 4-9 are for short to mid-term objectives (decade) with products designed in EU

#### 27 PARTNERS FROM 10 EU COUNTRIES

UNIVERSITÀ DI BOLOGNA

Faculty of Electrical

Engineering and

Computing

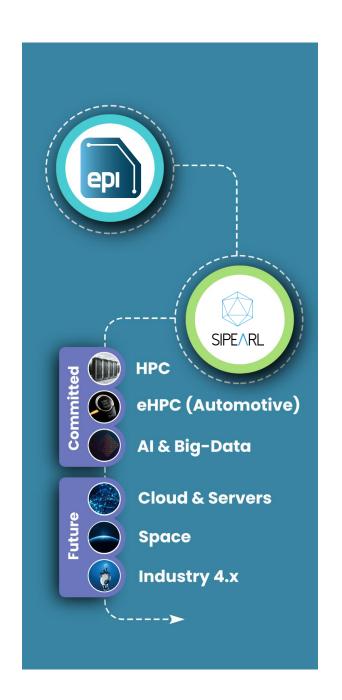

# FROM IPR TO PRODUCTS FROM EPI TO SIPEARL

- SIPEARL is

- Incorporated in EU (France)

- the industrial and business 'hand' of EPI

- the Fabless company

- licence of IPs from the partners

- develop own IPs around it

- licence the missing components from the market

- Raise in equity the missing budget (~100M€)

- generate revenue from both the HPC, IA, server and eHPC markets

- integrate, market, support & sell the chip

- work on the next generations

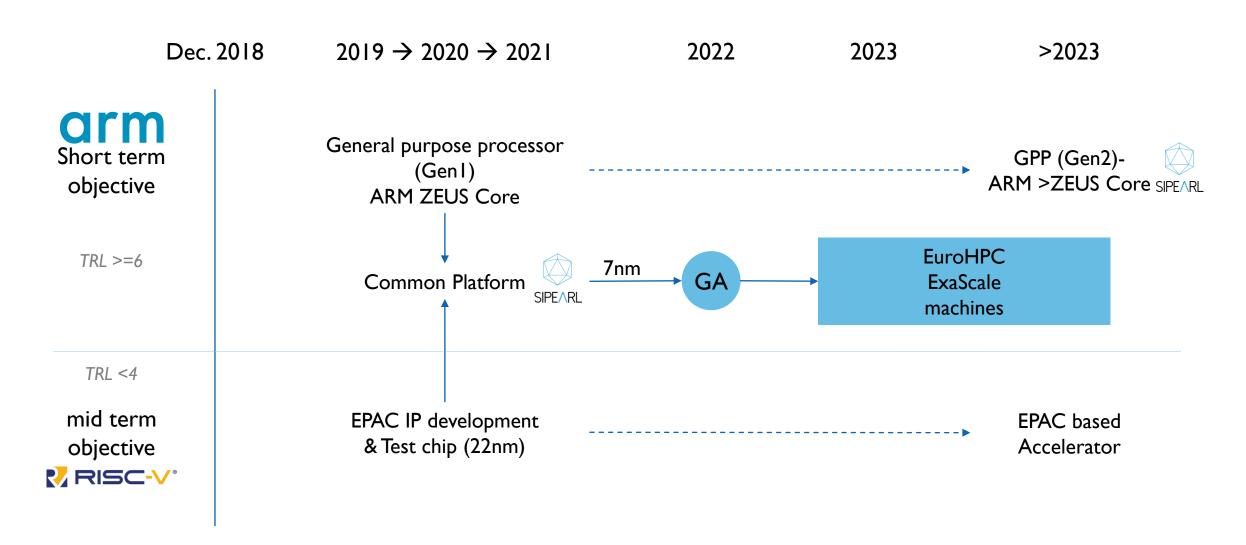

#### FROM OBJECTIVES TO ROADMAP, FROM ROADMAP TO PRODUCTS

# (POST)-EXASCALE SUPERCOMPUTERS OVERALL SPECIFICATIONS

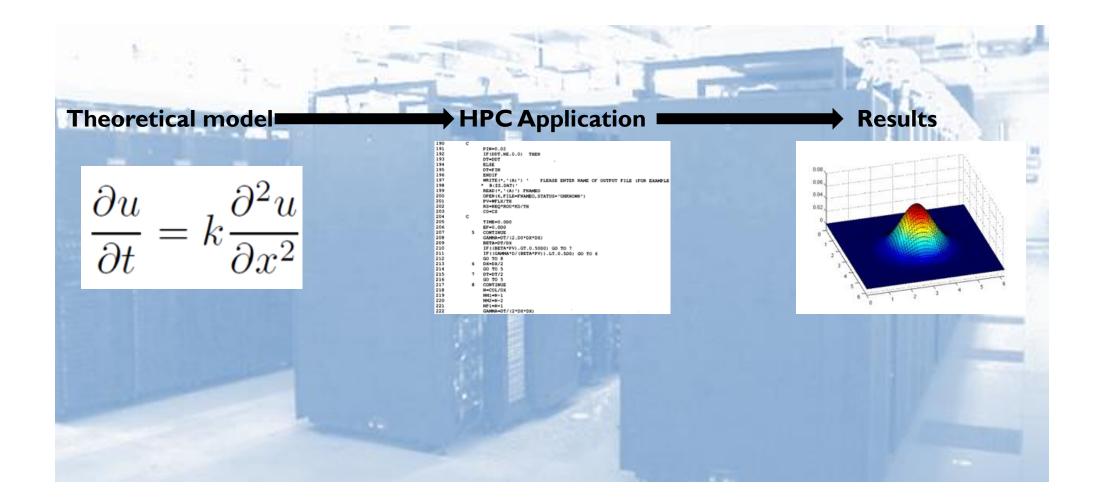

# HPC BEFORE ARTIFICIAL INTELLIGENCE

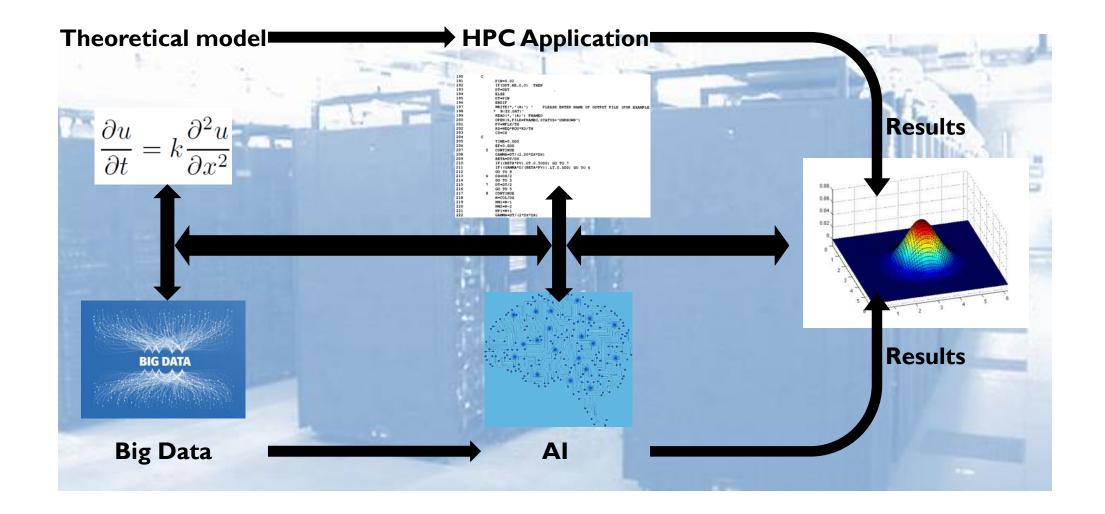

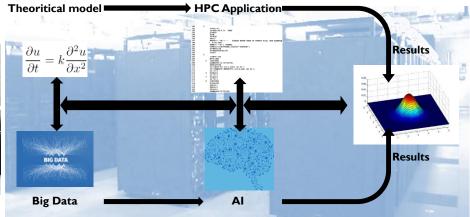

### HPC WITH ARTIFICIAL INTELLIGENCE

#### European Processor Initiative

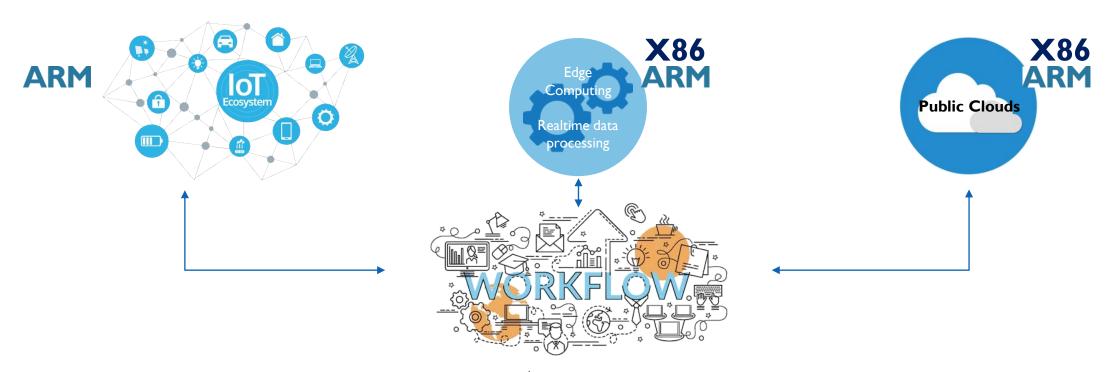

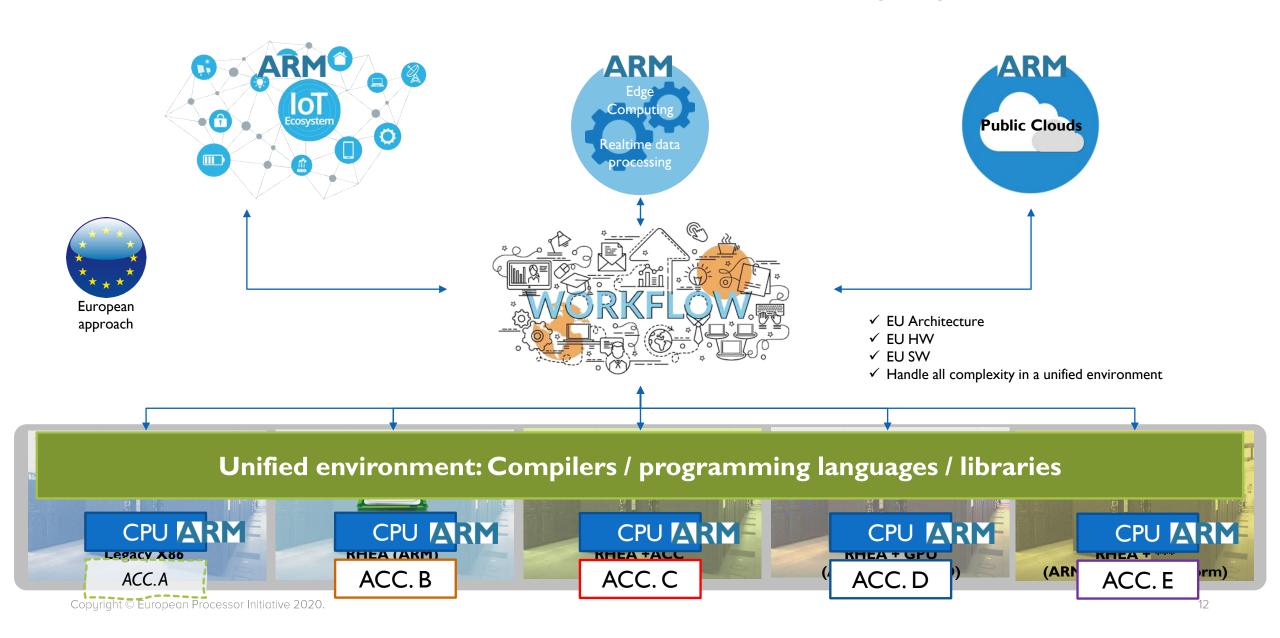

# HPC & AI AT EXASCALE: IT'S ALL ABOUT WORKFLOWS (1/3)

**SUMMIT**

#### sunway taihulight

# HPC & AI AT EXASCALE: IT'S ALL ABOUT WORKFLOWS (2/3)

#### European Processor Initiative

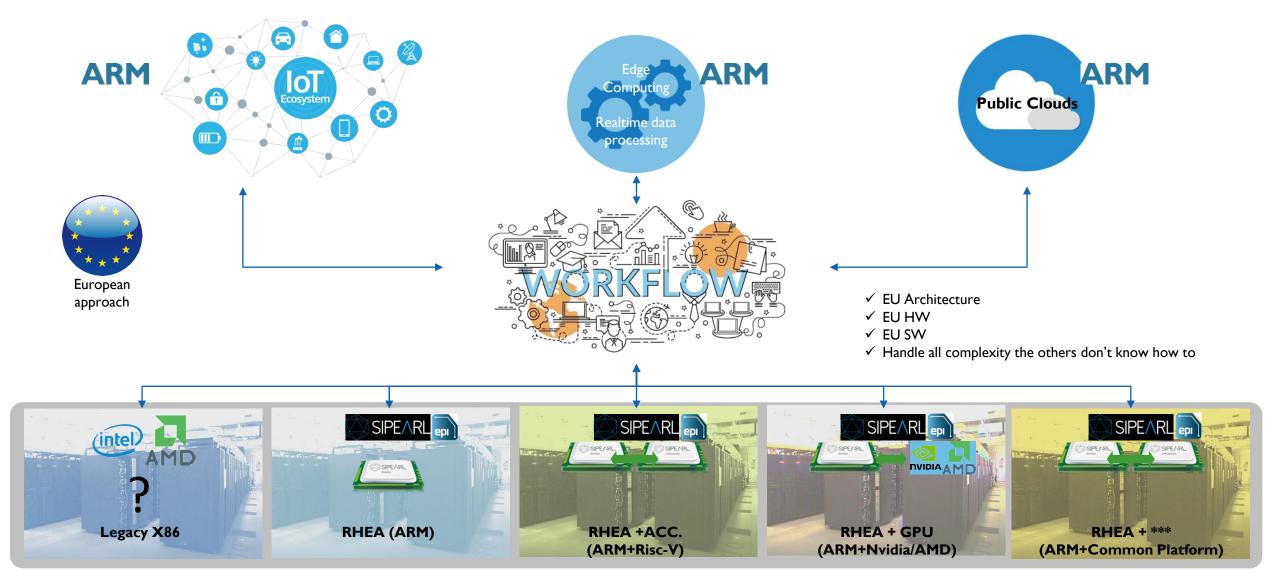

# HPC & AI AT EXASCALE: IT'S ALL ABOUT WORKFLOWS (3/3)

#### TAKEWAY #1

- The HPC Datacenter will

"disappear": users need a continuum

between sensors (IoT) and data

analysis (supercomputers) through

edge layer.

- Hybrid computing (in-house & Cloud) is a must

- Workflows from IoT to Supercomputers need seamless dataflows

- → develop once, run on many

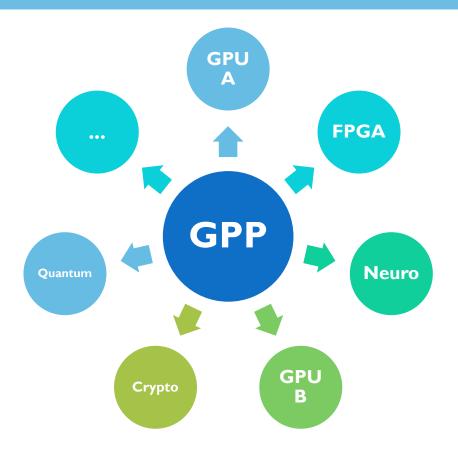

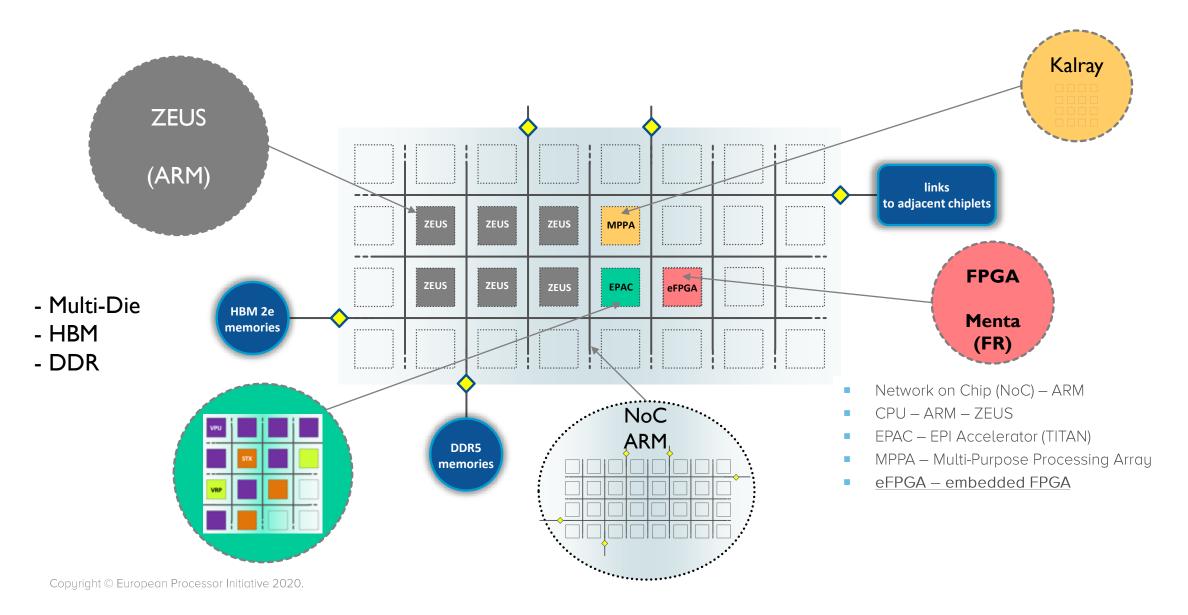

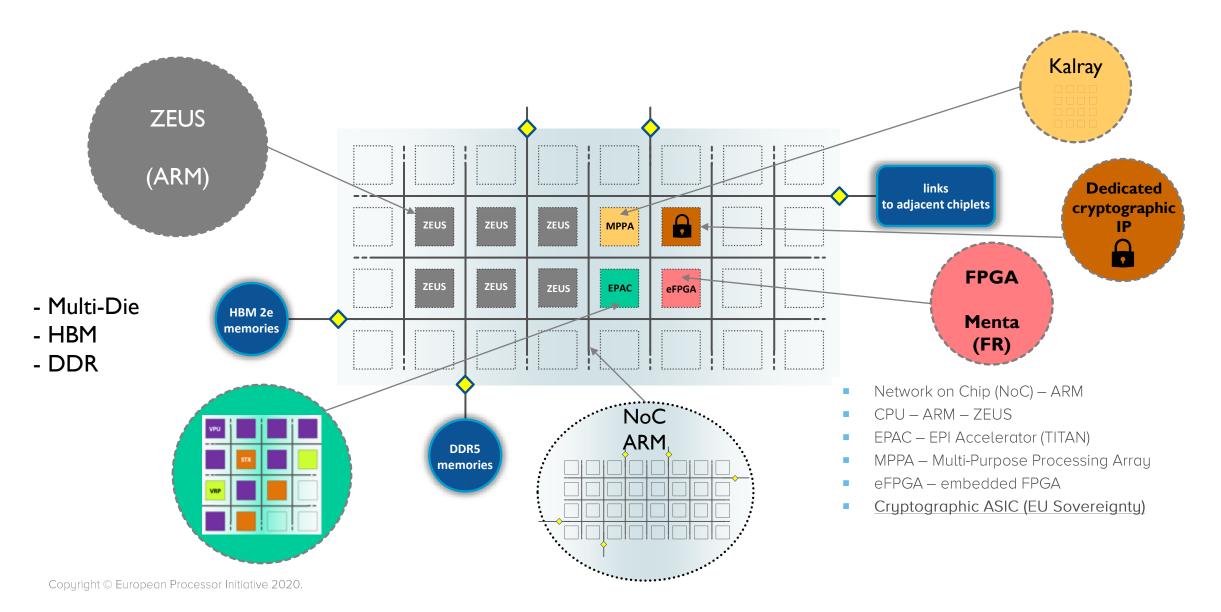

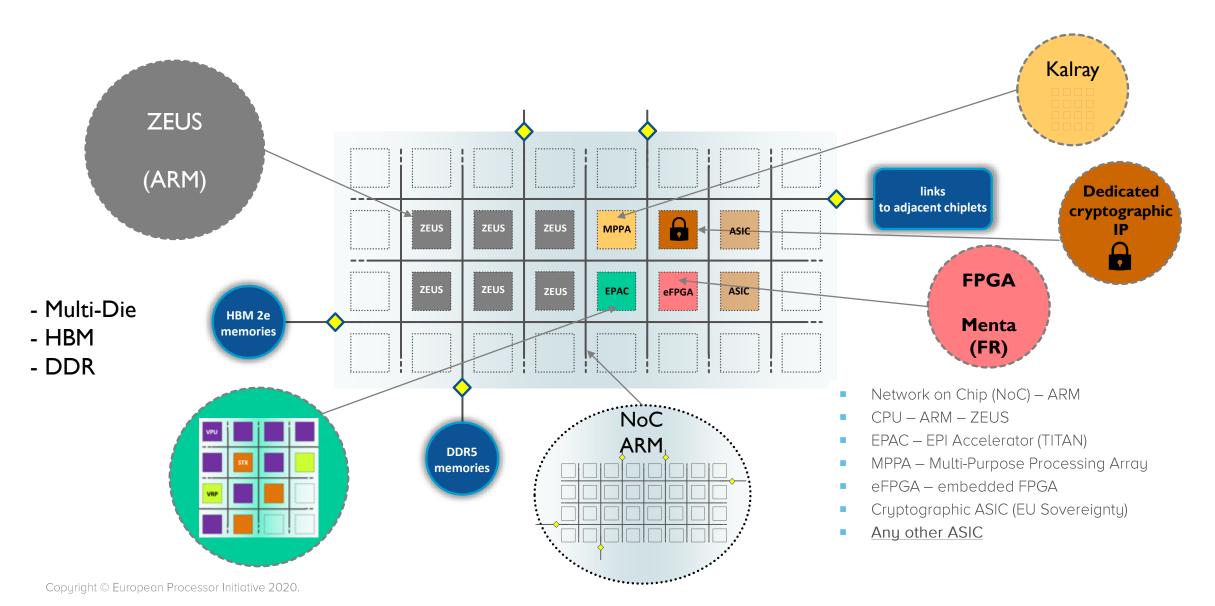

#### TAKEWAY #2

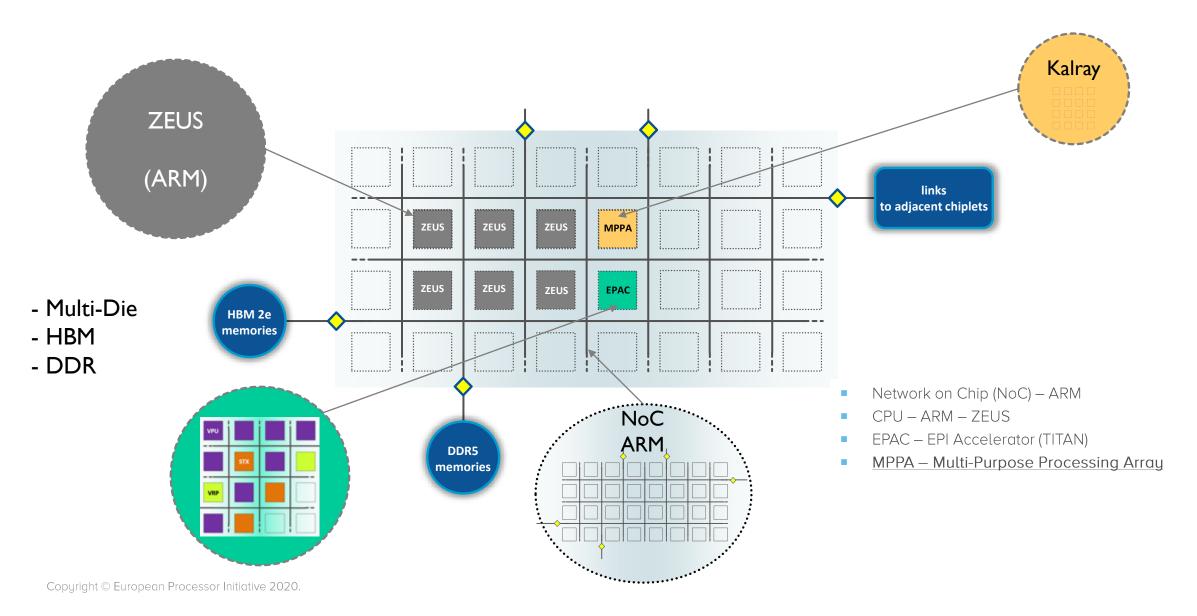

Exascale and post-Exascale superpercomputers will modular.

They'll have massively nonhomogenous architectures, combining one general purpose processor with several different accelerator kinds

#### TAKEWAY #3

Software will play an even more important role as a unification layer between all technologies, between all modules

- Opensource and standardization are more important than ever

- Proprietary SW stacks, especially for specialized HW will become problematic

# SPECIFICATIONS FOR AN EXASCALE CLASS GENERAL PURPOSE PROCESSOR

#### FROM TAKE AWAYS #1 TO #3

General Purpose Processors have to be (much) more open

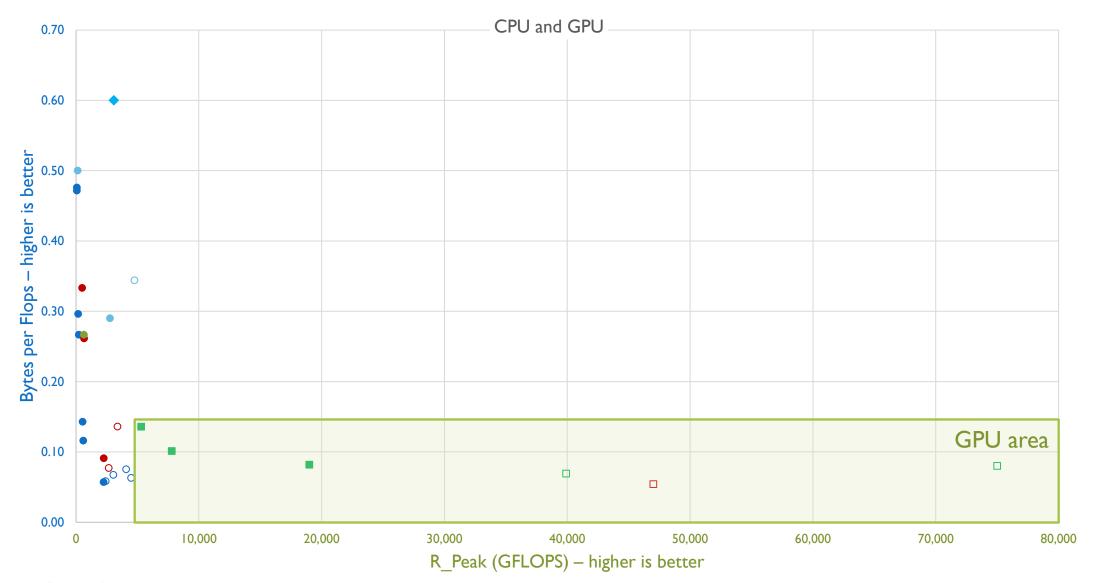

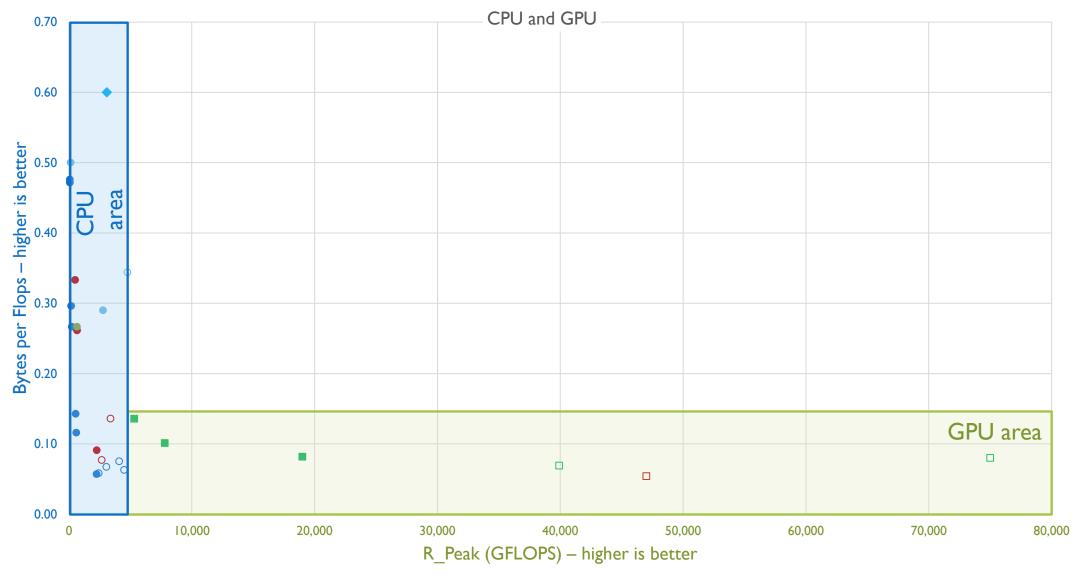

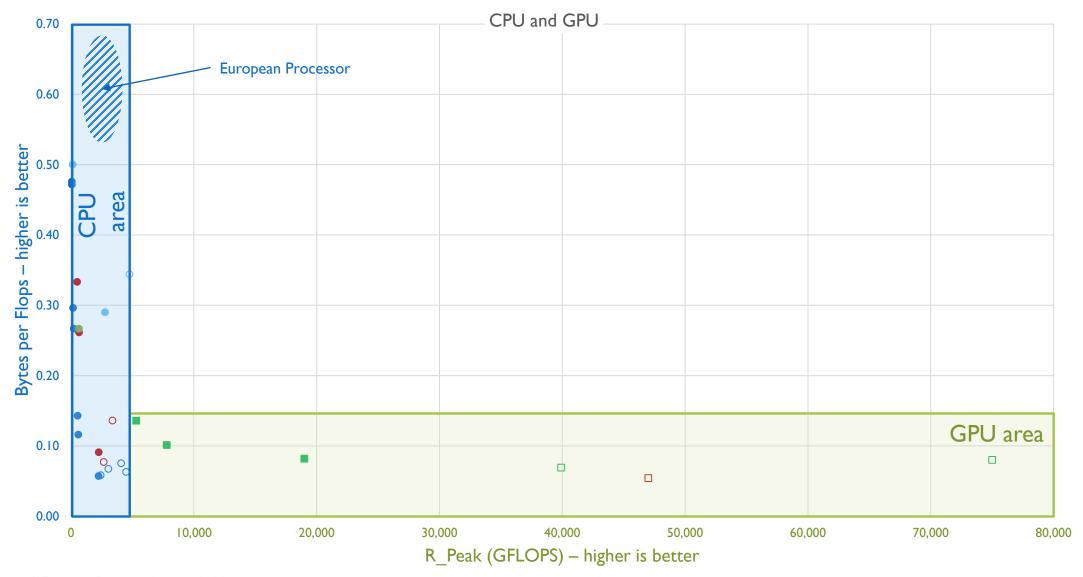

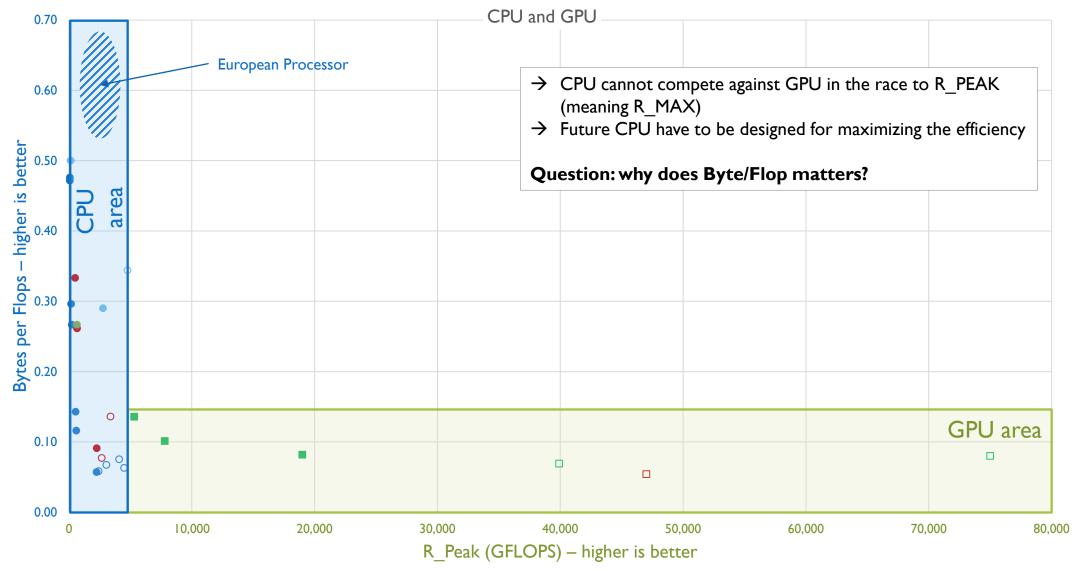

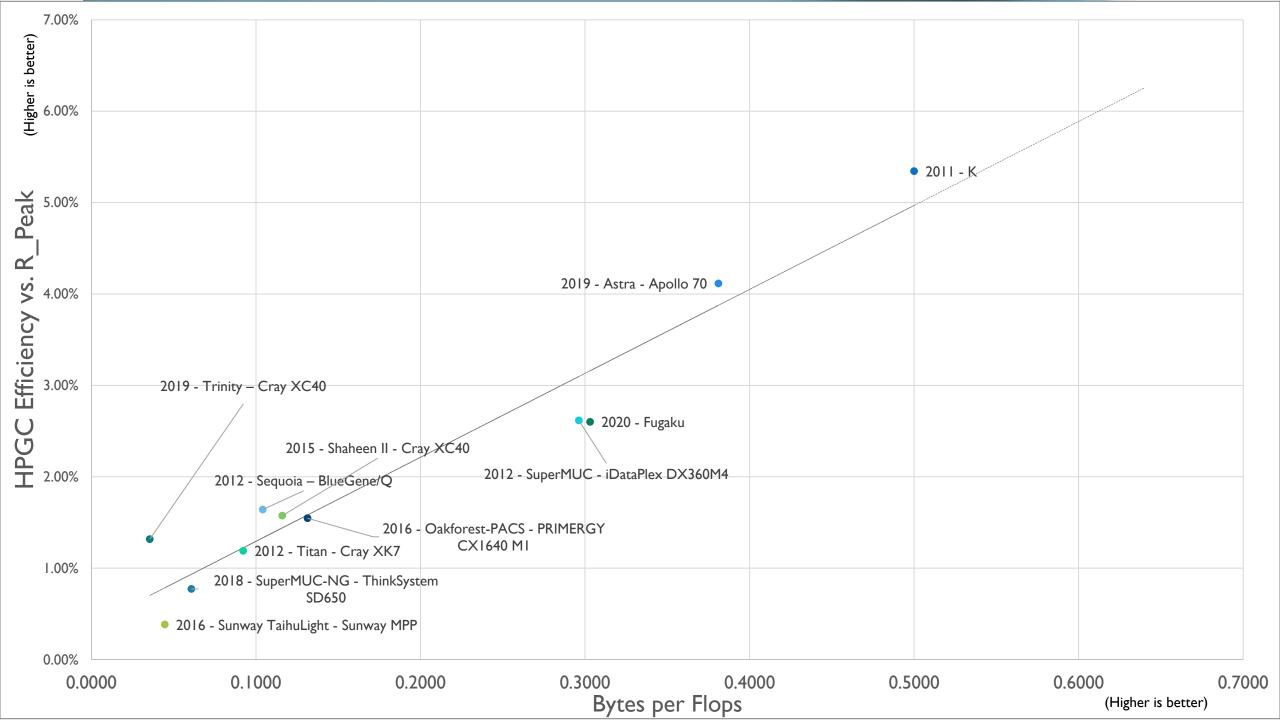

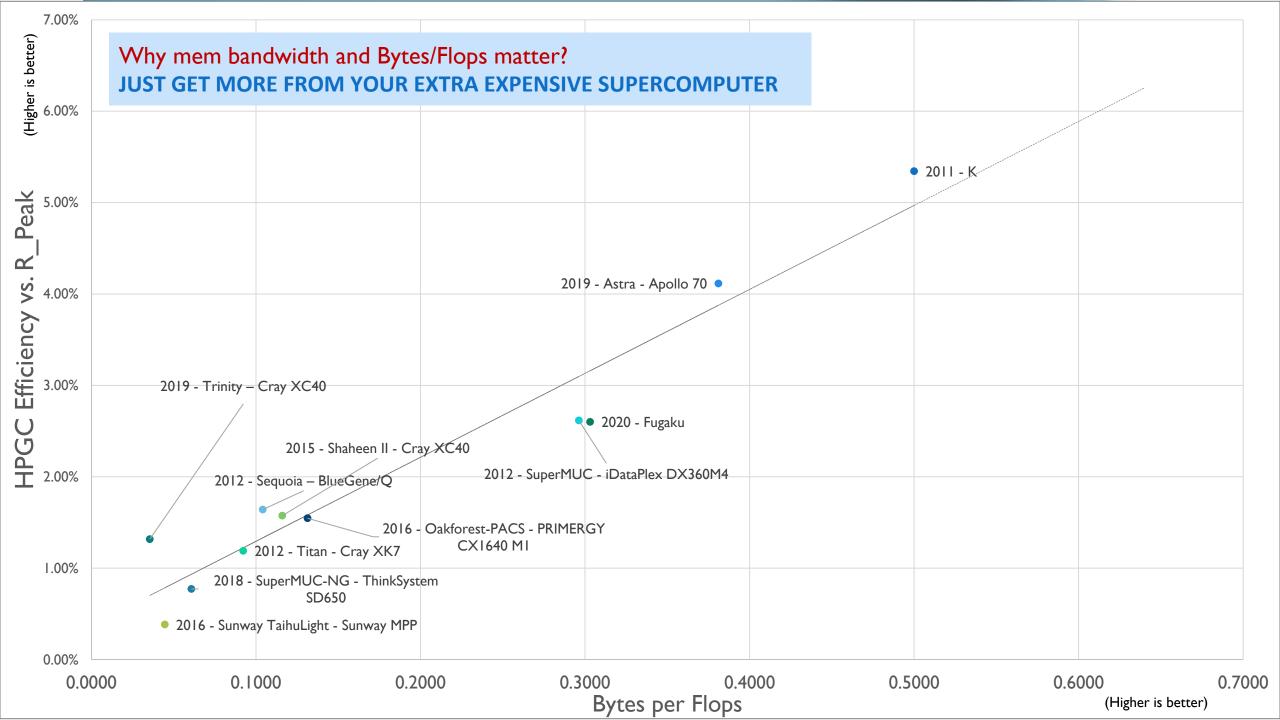

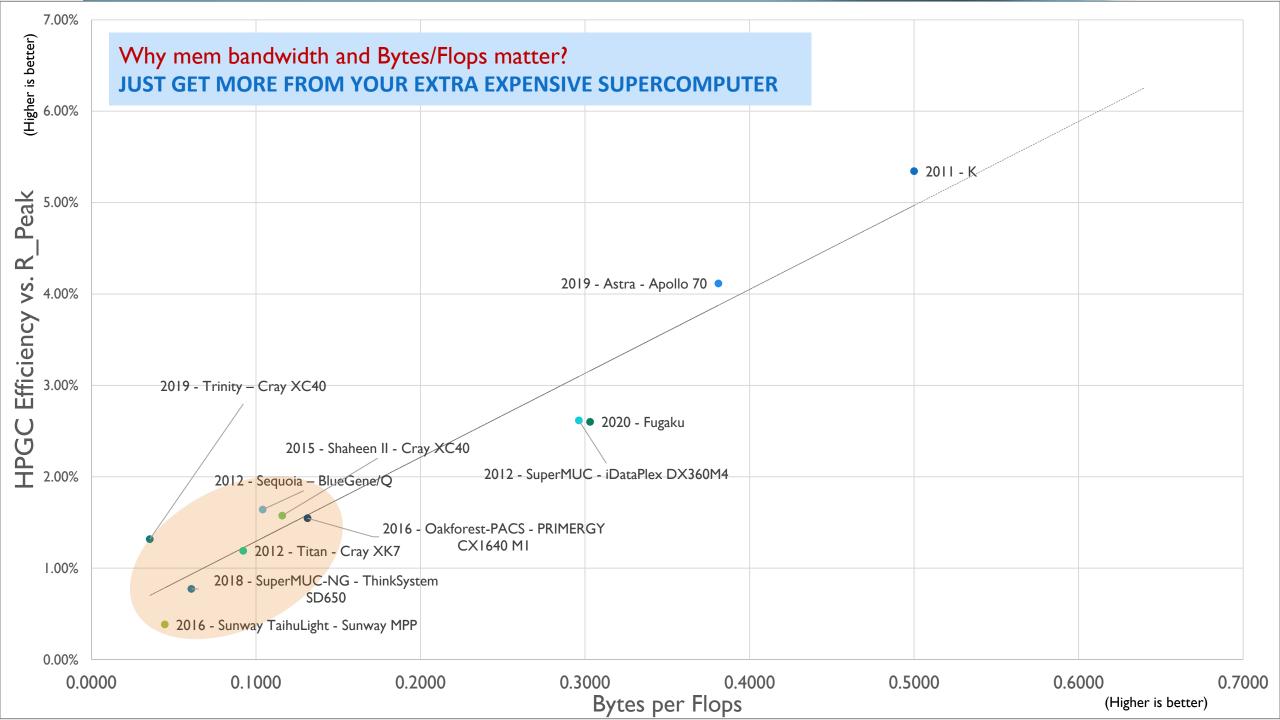

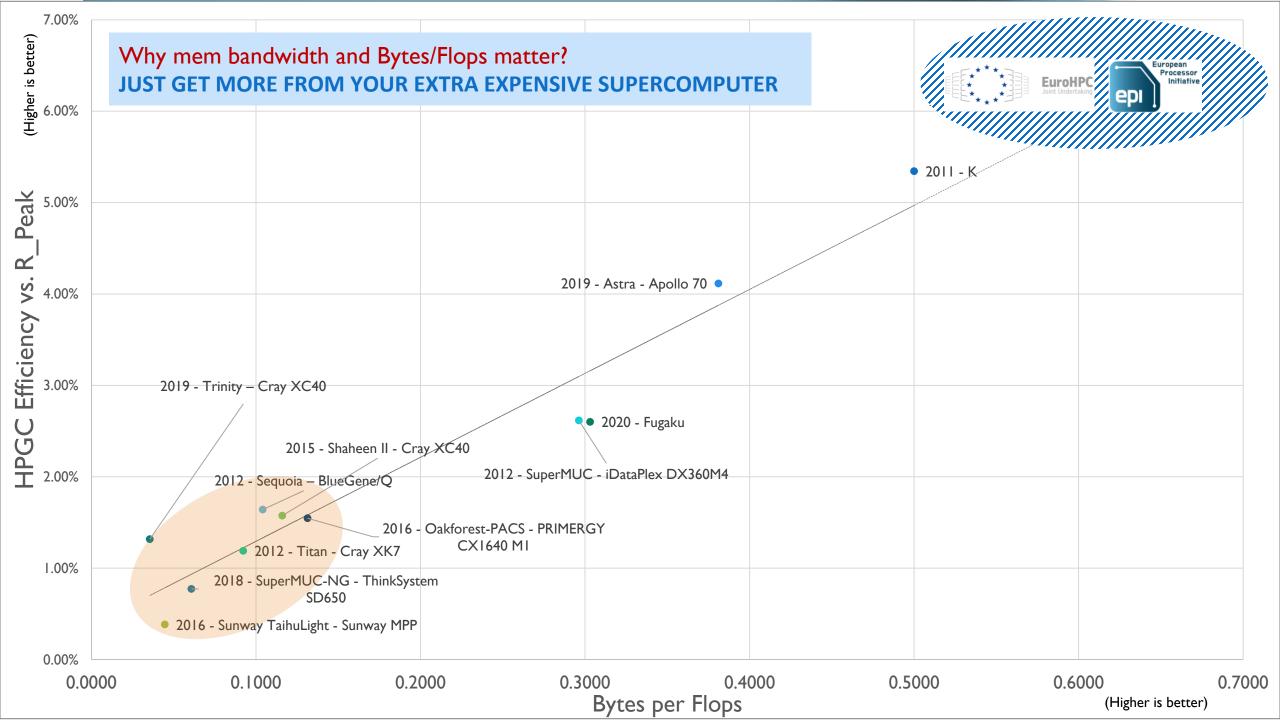

# The race to FLOPS is now in the accelerators area

# TAKEWAY #4 SPECIFICATION FOR EXASCALE GENERAL PURPOSE PROCESSORS (PART 1)

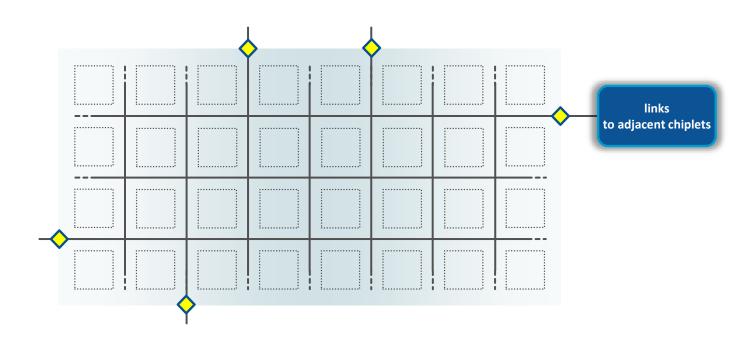

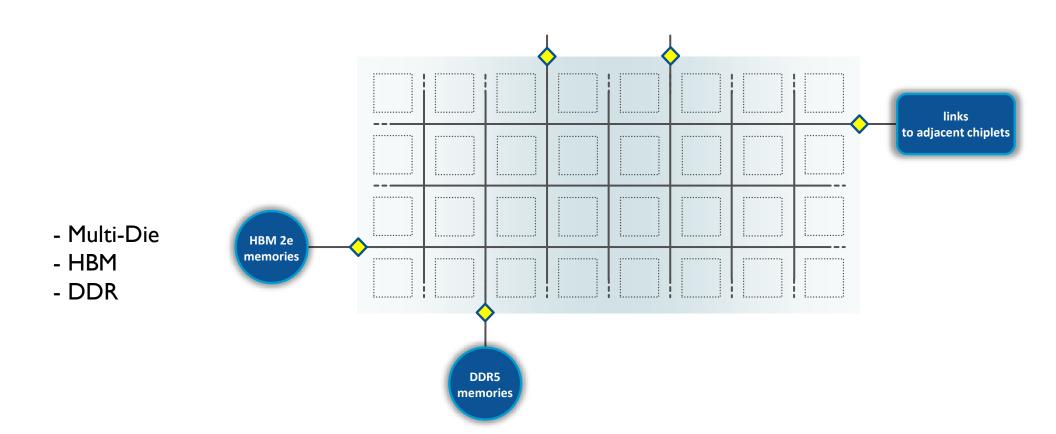

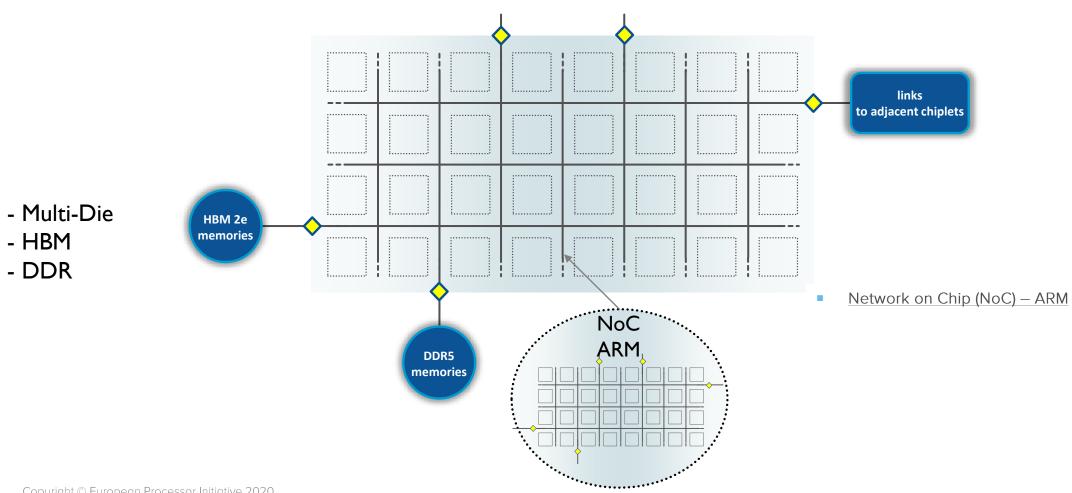

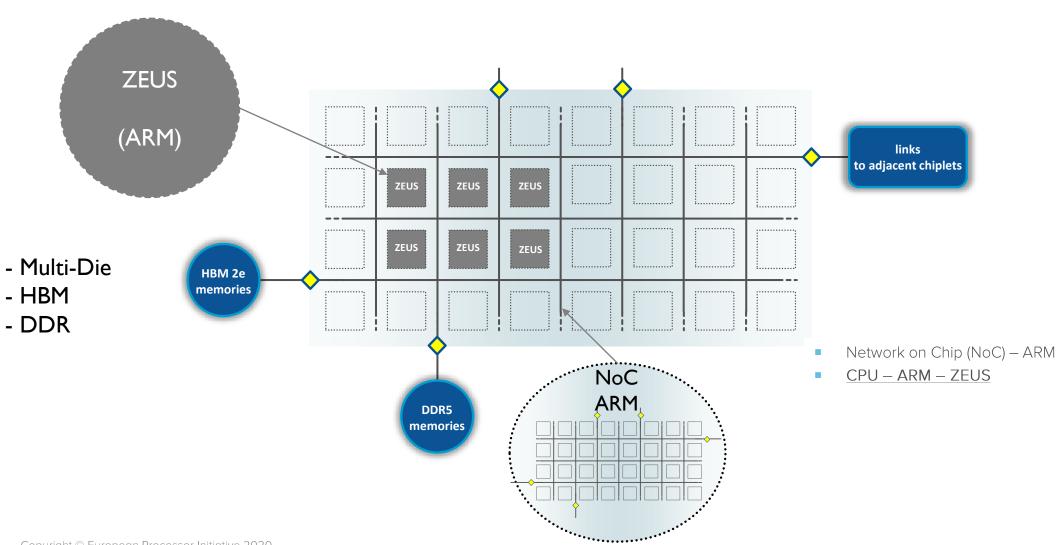

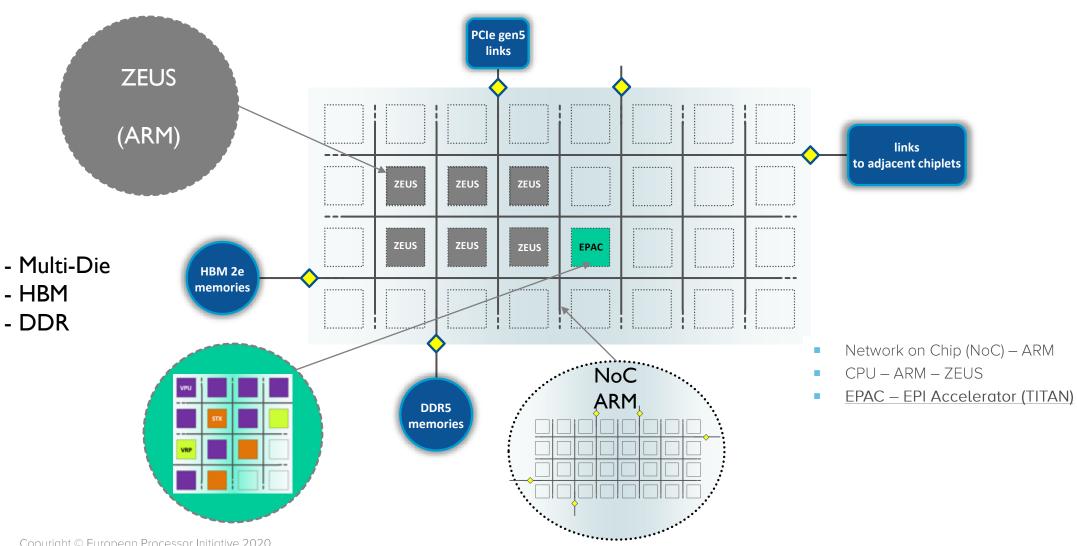

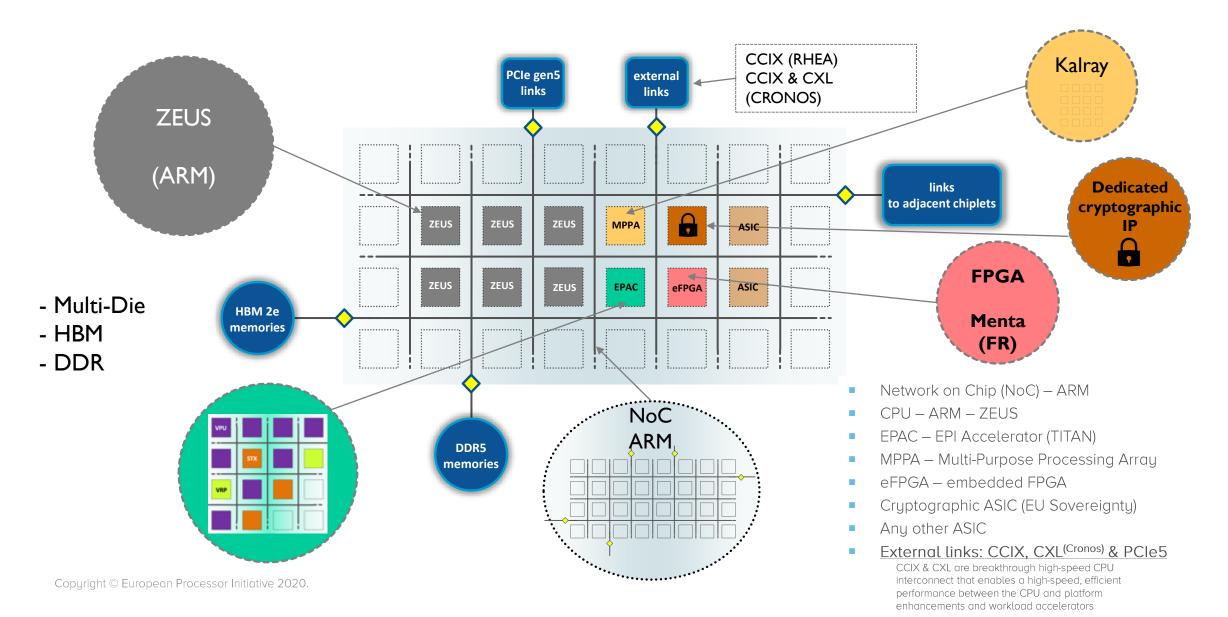

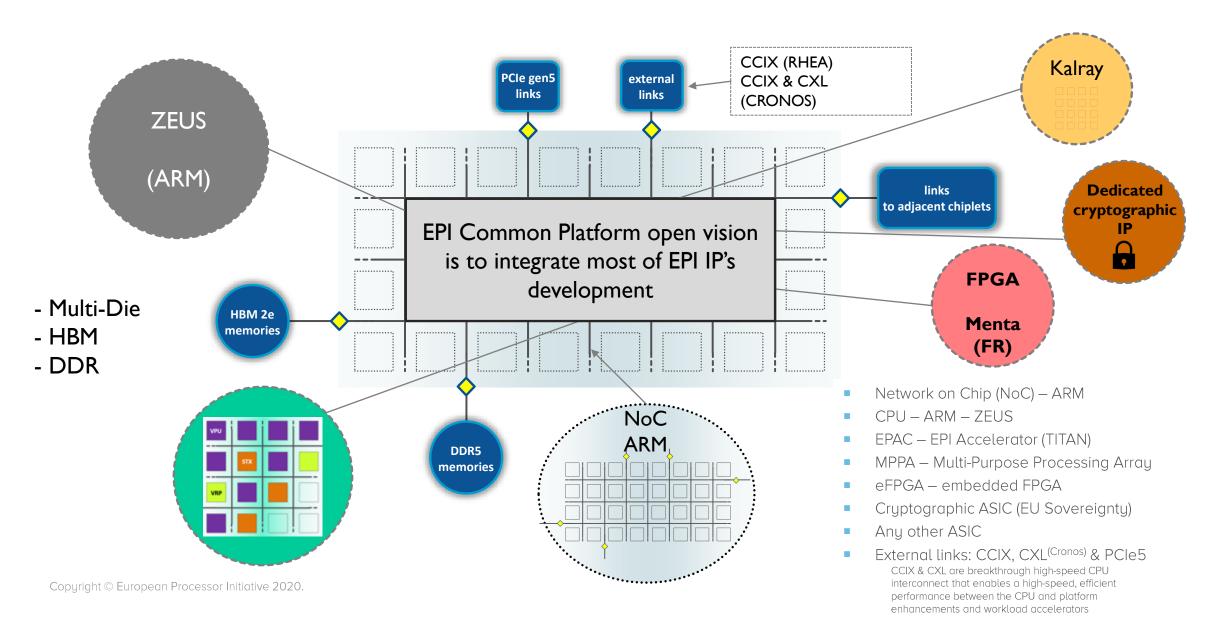

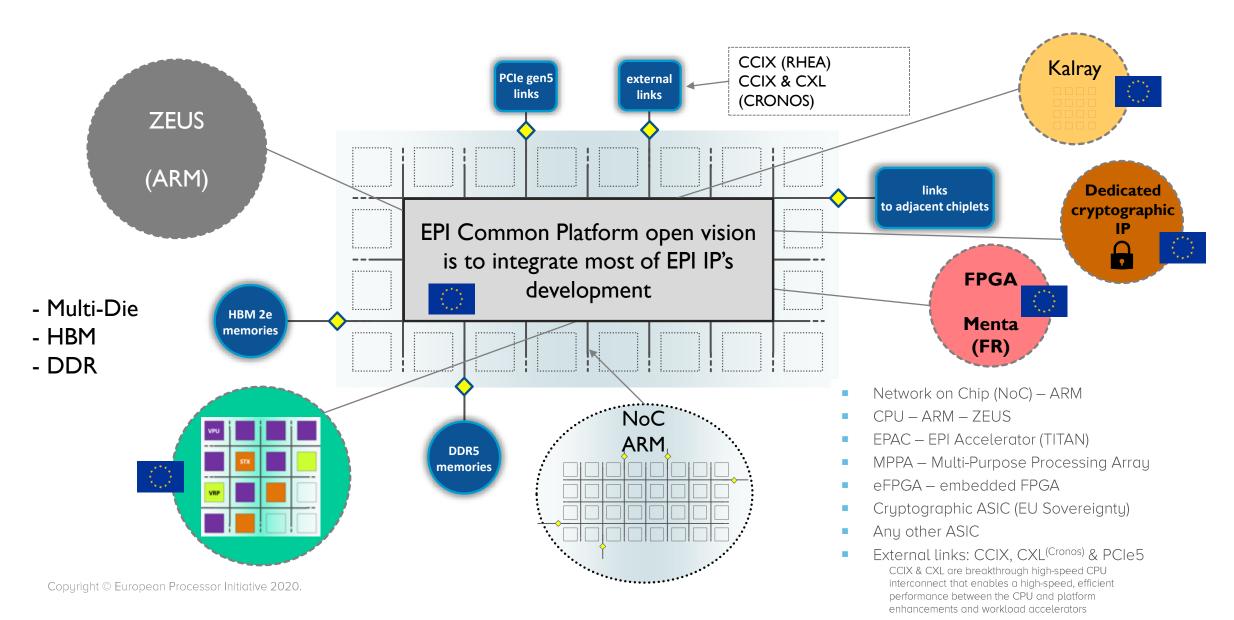

- Need extreme flexibility and performances on external links

- HBM 2e / 3

- \*and\* DDR 5

- \*and\* PCIe G5

- \*and\* CXL

- Transparent integration in end-to-end dataflow:

IoT ←→ Edge ←→ Datacenter ←→ Cloud

- Easy to port / optimize

- Opensource tools

- Unified development tools

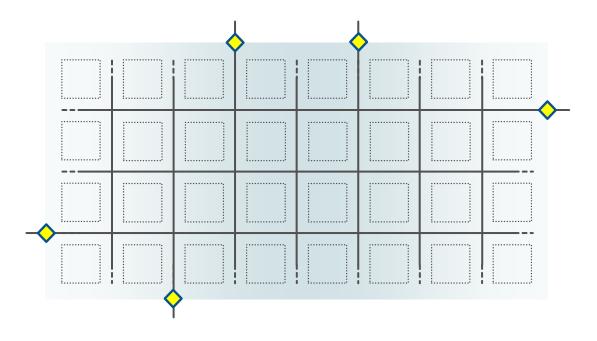

# EXASCALE CLASS GENERAL PURPOSE PROCESSORS UNDER THE HOOD

24

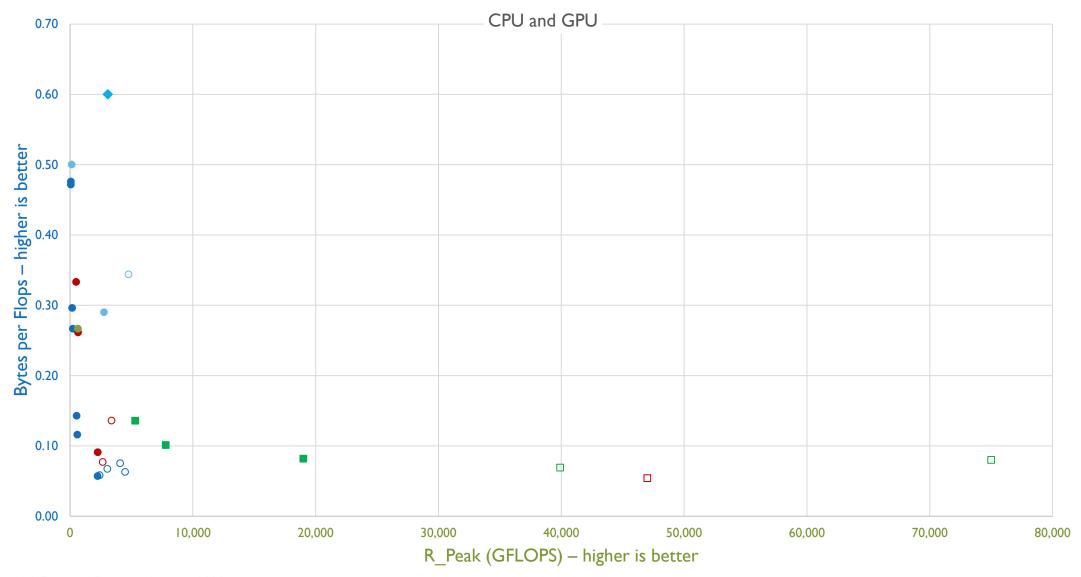

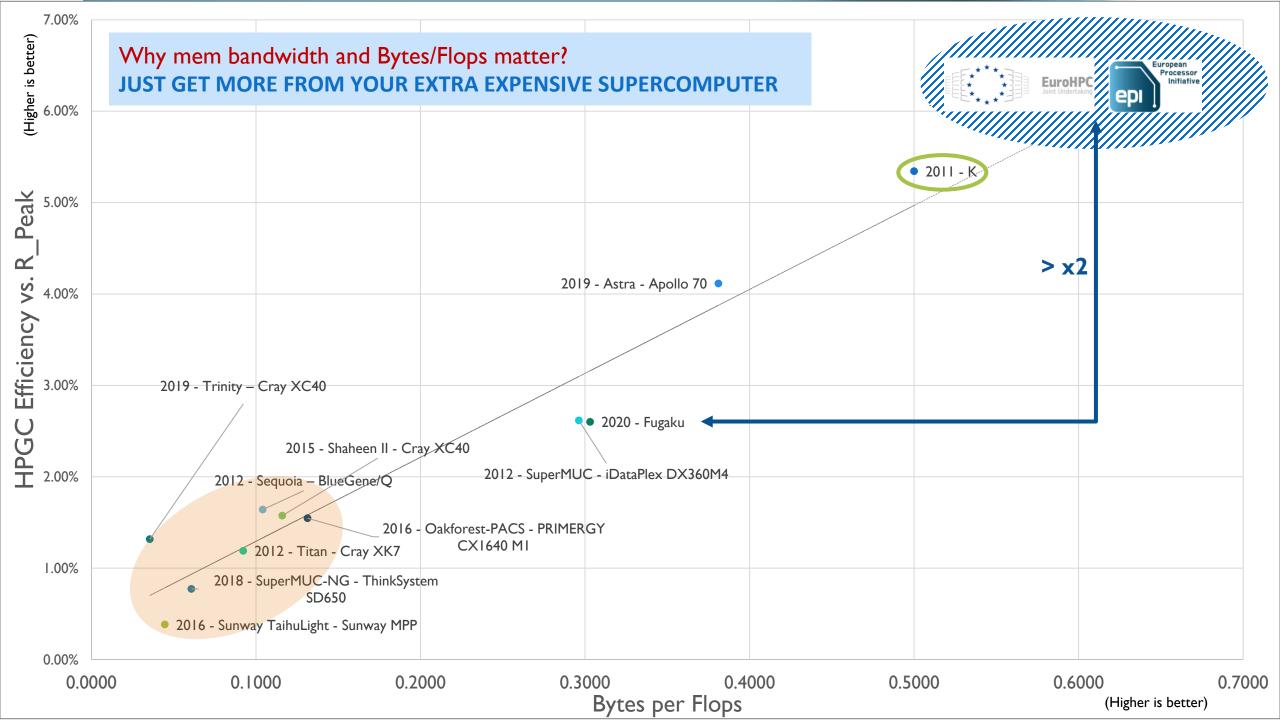

# TAKEWAY #5 SPECIFICATION FOR EXASCALE GENERAL PURPOSE PROCESSORS (PART 2)

- No need to compete with specialized devices like GPUs

- → Need "good enough" but excellent FP64 performances

- Improve overall efficiency

- → Need much better byte/Flop ratio than today

#### SO... WHAT ARE THE OVERALL SPECIFICATIONS FOR THE EUROPEAN PROCESSOR INITIATIVE?

- ARM Instruction set (IoT to HPC)

- Strong memory subsystem with HBM and DDR

- Extra large PCIe subsystem (maximize PCIe lanes)

- HPC standard interface (CXL)

- Maximum interoperability with accelerators

- Focus on ease of use

- +++ byte per flop

- +++ open source SW tools

- Multi-Die

Copyright © European Processor Initiative 2020.

# PERSPECTIVES AND CHALLENGES

#### **EPI DELIVERS!**

- The expertise for developing high-end and complex processing units in Europe, after decades of dis-investment

- A General Purpose Processor for HPC machines can be developed in EU by a EU Company (SiPearl)

- We'll be ready to move to the next step: engage on the development of a 100% EU IP general purpose processor.

Copyright © European Processor Initiative 2020.

#### **CHALLENGES?**

Copyright © European Processor Initiative 2020.

47

## **CHALLENGES?**

Copyright © European Processor Initiative 2020.

48

# THANK YOU FOR YOUR ATTENTION

- www.european-processor-initiative.eu

- @EuProcessor

- in European Processor Initiative

- European Processor Initiative