# FRAMEWORK PARTNERSHIP AGREEMENT IN EUROPEAN LOW-POWER MICROPROCESSOR TECHNOLOGIES

THIS PROJECT HAS RECEIVED FUNDING FROM THE EUROPEAN UNION'S HORIZON 2020 RESEARCH AND INNOVATION PROGRAMME UNDER GRANT AGREEMENT NO 826647

#### **EUROPEAN PROCESSOR INITIATIVE**

- High Performance General Purpose Processor for HPC

- High-performance RISC-V based accelerator

- Computing platform for edge and autonomous cars

- Will also target the AI, Big Data and other markets in order to be economically sustainable

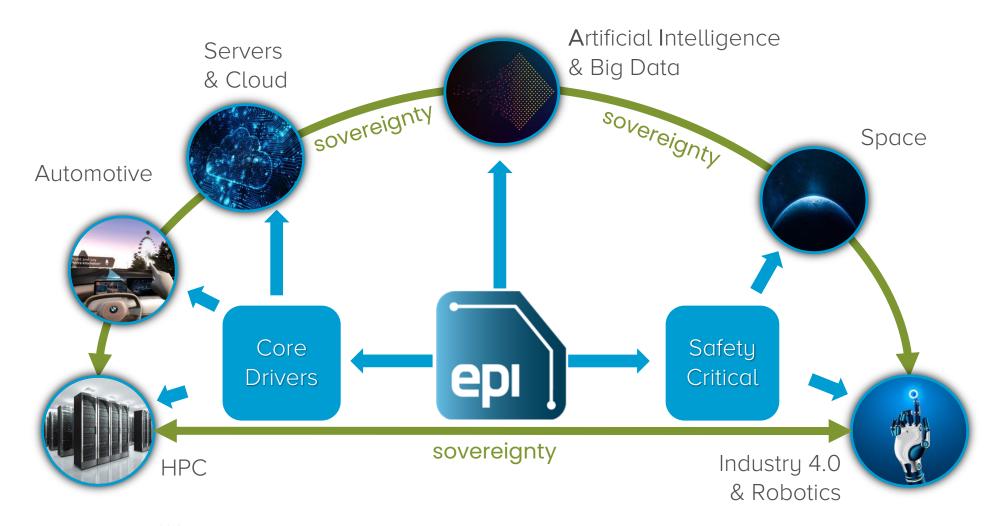

#### Overall objective

Enhance Europe's Technological Sovereignty in several key areas like HPC, Artificial intelligence, autonomous vehicles and edge computing

#### How?

Develop a complete EU-designed high-end microprocessor, addressing Supercomputing and edge-HPC segments

#### SCALABILITY ALLOWS WIDE MARKET POTENTIAL COVERAGE

Copyright © European Processor Initiative 2019

#### EPI: 27 PARTNERS FROM 10 EU COUNTRIES

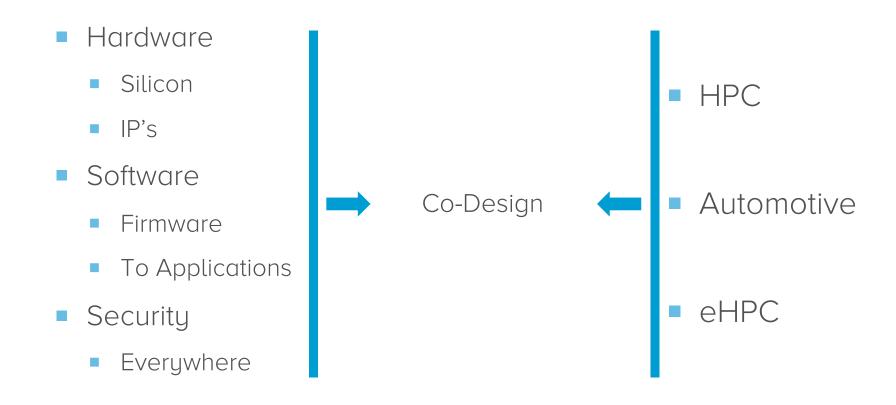

#### EPI KEY ELEMENTS & GUIDELINES

Copyright © European Processor Initiative 2019.

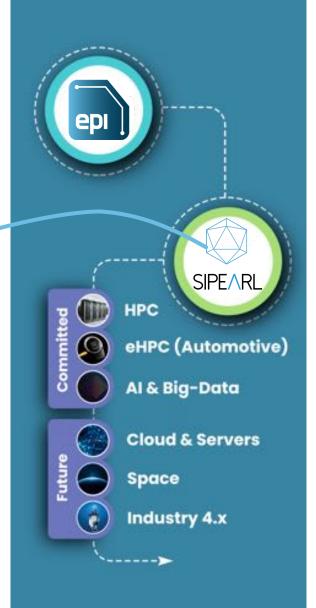

# FROM IPR TO PRODUCTS FROM EPI TO SIPEARL

- SIPEARL is

- Incorporated in EU (France)

- the industrial and business 'hand' of EPI

- the Fabless company

- licence of IPs from the partners

- develop own IPs around it

- licence the missing components from the market

- Raise in equity the missing budget (~100M€)

- generate revenue from both the HPC, IA, server and eHPC markets

- integrate, market, support & sell the chip

- work on the next generations

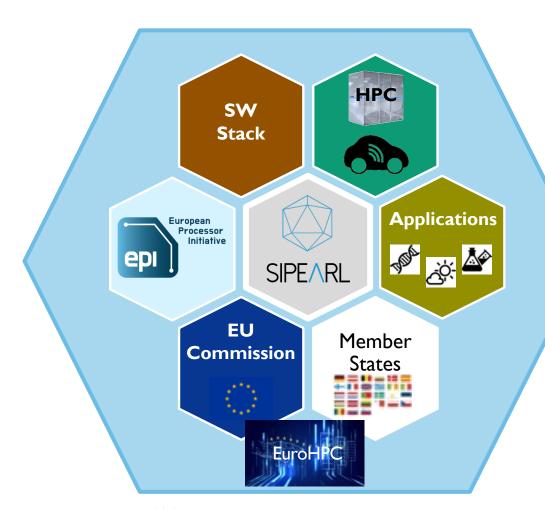

#### EPI & SIPEARL ARE THE EUROHPC INDUSTRIAL CORNERSTONE

April 2016

- « foster an HPC ecosystem capable of developing new European technology such as low power HPC chips »

- « ...acquisition of two co-design prototype exascale supercomputers in 2020, at least one based on European technology, which will rank in the Top3 of the world »

### **ROADMAP & TECHNOLOGY**

with RHEA β version

#### EPI IP's Launch Pad ROADMAP **ZEUS** Core Pan European Research TITAN Acc. Platform for HPC and Al 5nm Gen3 GPP Family 2021 2022-2023 2021-2022 2024-... Rhea Family - Gen1 GPP Cronos Family - Gen2 GPP **ZEUS Core** <u>2022 – H2</u> EPI Common Platform EPI Common Platform 6nm ARM & RISC-V ARM & RISC-V **EU Exascale Supercomputer** External IPs Edge-HPC (autonomous vehicle) HPC System Exascale with CHRONOS & TITAN HPC System PreExascale Automotive CPU Automotive PoC <u>2021 – H2</u> E4 - PCle board (WS compatible) SIPEARL SIPEARL SIPEARL ATOS - BullxSequana Board

Copyright

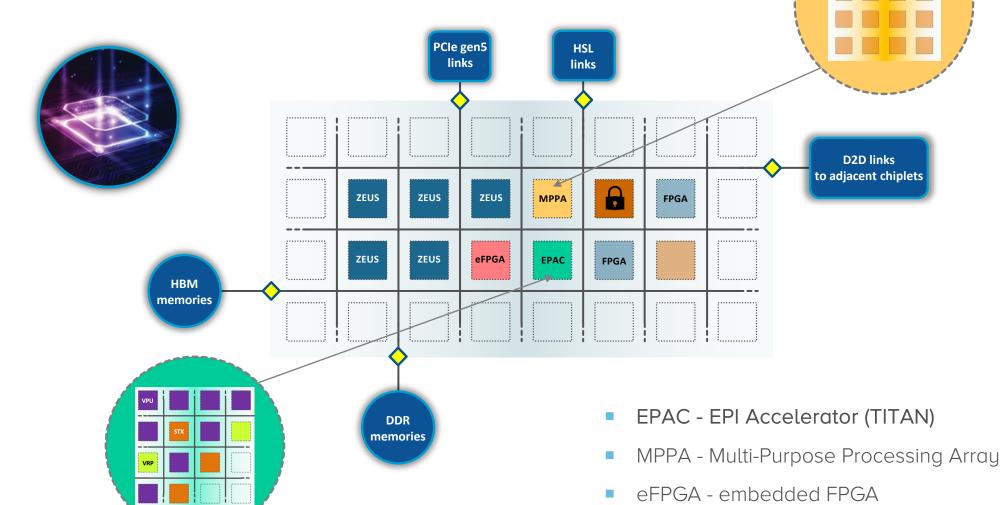

#### GPP AND COMMON ARCHITECTURE

Copyright © European Processor Initiative 2019.

Cryptographic ASIC (EU Sovereignty)

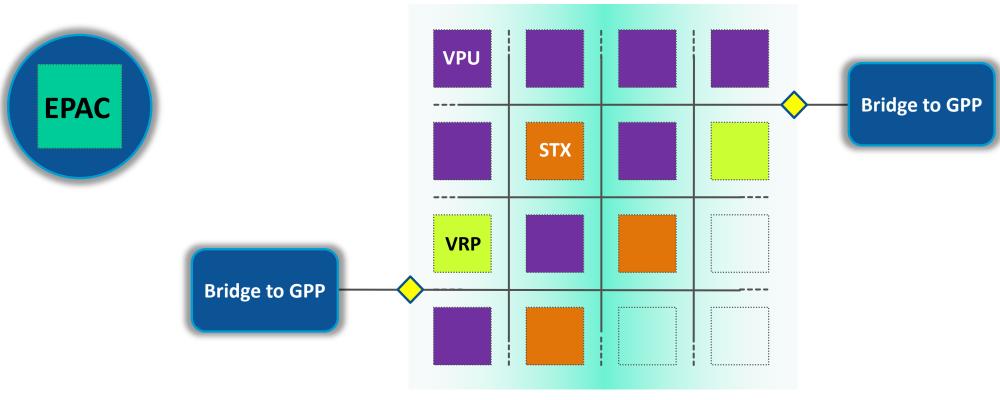

#### EPAC - RISC-V ACCELERATOR

- EPAC TITAN = EPI Accelerator

- VPU Vector Processing Unit

- STX Stencil/Tensor accelerator

Copyright © European Processor Initiative 2019.

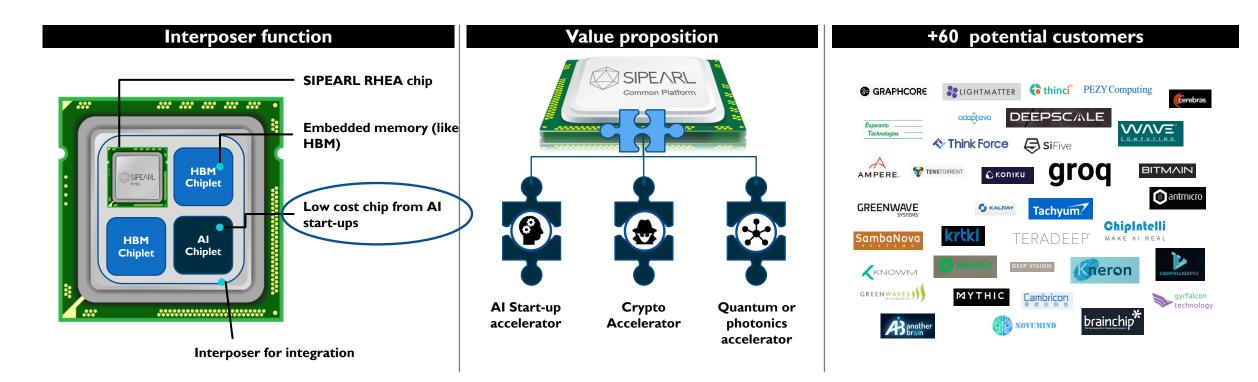

#### COMMON PLATFORM VISION: WE ACCELERATE ACCELERATORS

# COMMON PLATFORM HAS THE POTENTIAL TO BE COME THE EUROPEAN I/O STANDARD DATA-PROCESSING

## **SOFTWARE**

**TECHNOLOGY**

#### HOLISTIC APPROACH

- Build on successful existing approaches

- Node administration → ARM +Open BMC

- Operating system → Linux

- Security by design → protect data (GPRD)

- Compilers → GCC & LLVM

- Libraries (HPC / AI / Edge / Automotive)

- Development environment

- GPP & ACC → OpenMP

On EPI own budgets

Partnership

is key

EuroHPC RIA (calls 2019)

Prepare EU Exascale EuriHPC landing

Copyright © European Processor Initiative 2019.

14

#### EPI SOFTWARE AMBITIONS IN HPC

- Complement the already existing software to supply an entire HPC production stack

- Deployment/administrative side

- Securing the node

- Power managing the node

- Booting the node

- (Remote) controlling the node

- Running a Linux distribution on the node

- Managing various nodes in a large system

- Monitoring & accounting various nodes in a large system

#### End-user side

- Compiling software for the General Purpose Processor

- Compiling software for the Accelerators

- Combining the use of GPP & Accelerators in a software

- Leveraging standard libraries tuned for the node

- Running the software on a node

- Running the software on multiple nodes in a system

#### Automotive (edge-HPC) requirements

- Security, power

- Predictable performance for autonomous driving

- Multiple inputs, complex models

#### **ARM WW HPC**

**CPU** manufacturer, 2 server manufacturers, "Astra" system at Sandia, upcoming system at Stony Brook

**Upcoming CPU** manufacturer, Server manufacturer, system at CEA, UK, MontBlanc, EPI

> CPU & server manufacturer, upcoming "Fugaku" system

CPU & server manufacturer [geopolitical issues regarding the license]

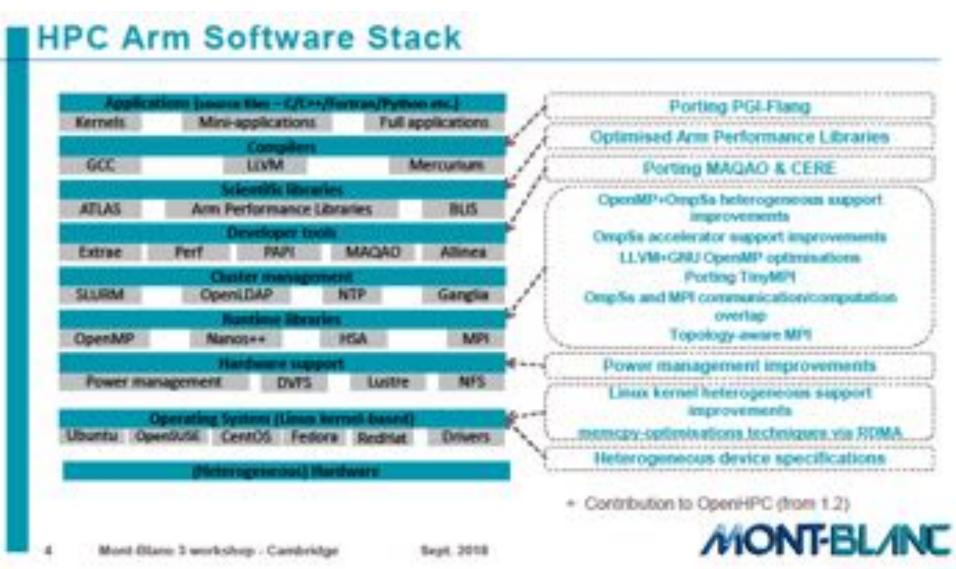

#### STANDING ON THE SHOULDERS OF SUCCESSFUL EUROPEAN PROJECTS

Mont-Blanc 3

helped create

and stabilize

most of the

foundations

of a full HPC

software

stack on Arm

#### **EPI ECOSYSTEM**

(INCLUDING POTENTIAL OUTSIDE PARTNERS)

**EPI Reference Hardware**

#### **EXPANDING TO RISC-V**

- The RISC-V architecture is used extensively in EPI

- EPAC accelerator, Power Management, ...

- It is fully open and not reliant on one company for its definition

- The software ecosystem is not yet has developed as the Arm one

- Mont-Blanc projects were instrumental in maturing the Arm ecosystem

- EPI software work includes work to bring RISC-V closer to the need of a production-ready general-purpose processor

- MPI work on RISC-V & hybrid

- OpenMP runtime on RISC-V

- For offloading & native mode

- Compiler work

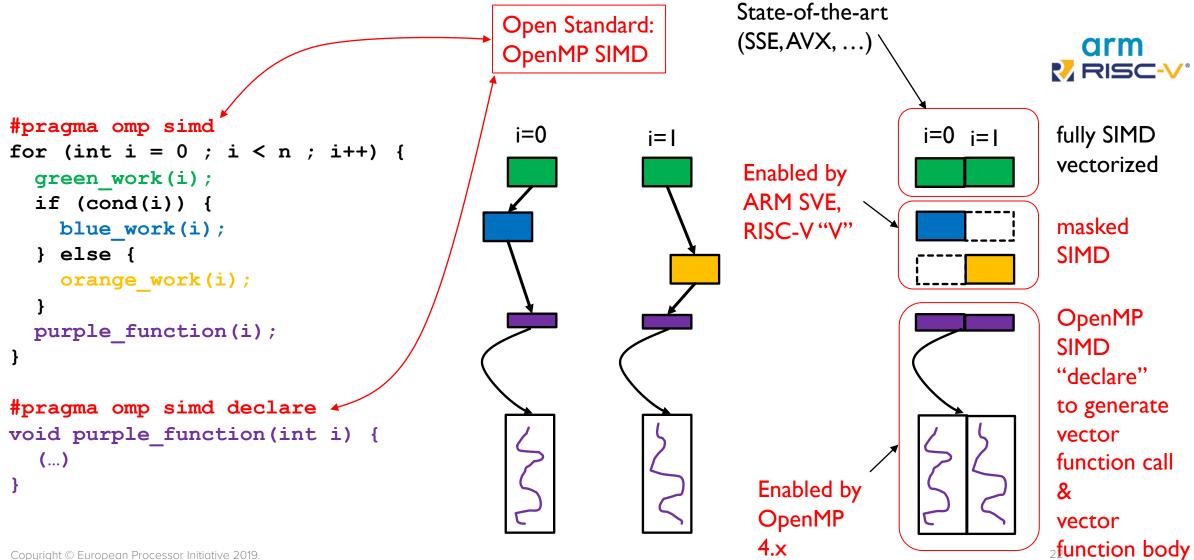

- Including OpenMP SIMD

- Using RISC-V in the industrial world as a fullfledged, linux-capable processor and not just a microcontroller

- Real-life use to strengthen the software

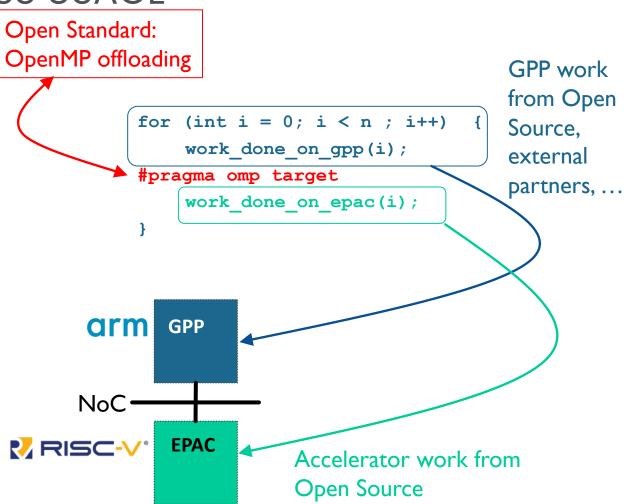

### END-USER: GPP/ACC SEAMLESS USAGE

- Compiling, combining

- Leveraging work from existing Open Source projects: GNU, LLVM

- Choosing open standard over proprietary solutions

- Emphasis on OpenMP in the project

- OpenVX for automotive

- Working with external partners

- Arm work in LLVM & libraries for the GPP

- EPI adding missing pieces to fully exploit the Common Platform design

- Better vectorization in EPAC

- OpenMP offloading

- OpenMP SIMD for EPAC

#### END-USER: COMBINE SIMD W. VECTORIZATION

## **EPI FOR EDGE**

Copyright © European Processor Initiative 2019.

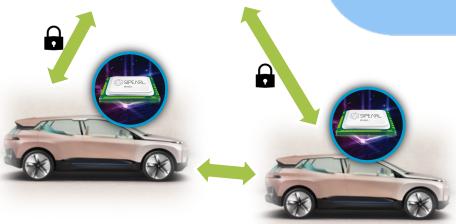

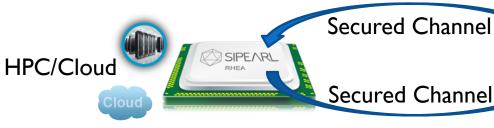

#### END TO END SECURED EDGE COMMUNICATIONS

END2END SECURITY FROM THE AUTOMOT

**CLOUD**

Secure channel Backdoor free EU encryption

#### SECURITY BY DESIGN

#### **High Speed**

- High Speed Encryption/Decryption

- Highly confidential Authentication

- Low Latency. Save 5G low latency value

# Embedded w. compute

- Prevents 'easy access' to explicit content

- Final decryption is directly managed by the computing core, inside the chip

- Limits any physical attack in the Car hardware (inspired by PayTV technologies)

- SiPearl cryptoblocks's certification embedded n all products allows easy Full chain certification

#### **GDPR** Compliant

- Data's are fully protected end2end

- Even a compromised 5G network cannot see the data's

# Long term protection

- Prevents any nonauthorized upgrade for future-proof car use

- Dangerous hacking

- Engine mods

- Car stealing

- Secure upgrade of critical soft components

- Secure boot for code integrity

- Resistant to physical attack

edge

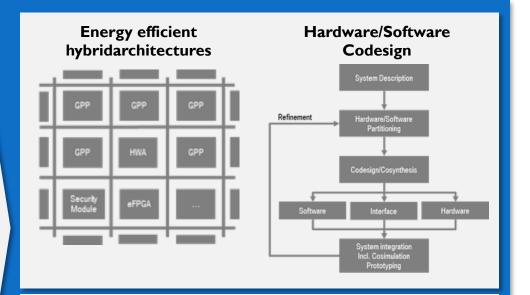

#### TAKING HPC FROM CONSUMER TO AUTOMOTIVE

#

- Automotive MC (µCs) are suitable for basic funktions (e.g. brake)

- Plain usage of consumer μCs not helpful

- New hybrid approaches are necessary

#### **Energy = Distance**

- Tesla and Apple saw the potential and develop their own chips

- E.g. Apple iPhone 8 needs only half battery capacity for same active time compared to Samsung

- Hybrid architektures enable energy efficient compute power by optimal balance between General Purpose Processors (GPP), accelerators and programmable Hardware (eFPGA).

- Hardware/Software Codesign helps to find the otimal balance.

Copyright © European Processor Initiative 2019.

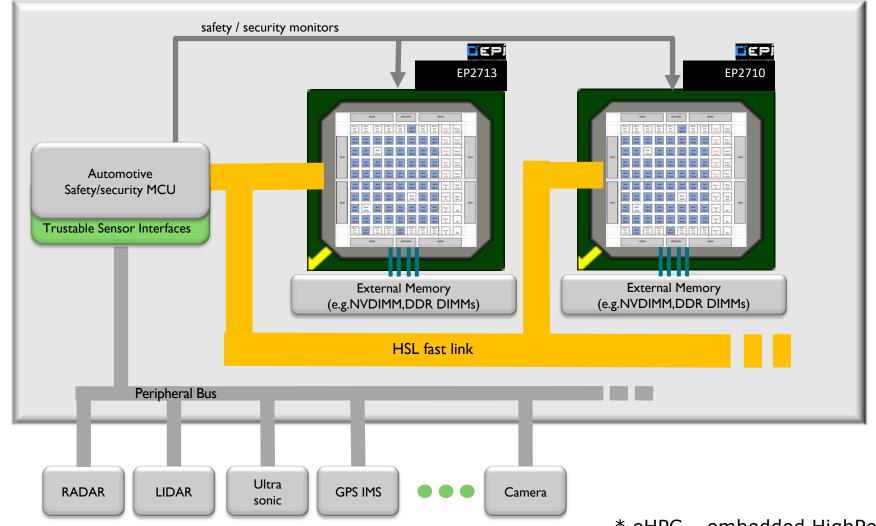

#### AUTOMOTIVE EHPC PLATFORM

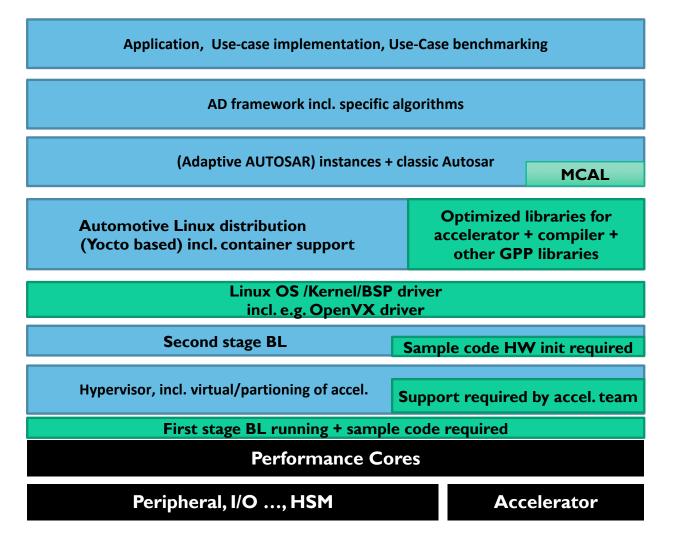

#### AUTOMOTIVE SPECIFIC SW STACK

#### Automotive specific

- Reference boards

- Linux config, patches

- Extended BSP for RefBoard

- Automotive Middleware, protocols and libraries

- Everything around AUTOSAR

- AD framework + benchmarking

- Automotive Demo use case

- Integration and interaction with Safety Chips from Info

- Integration in BMW demo

- ...

# Take over assumption from other EPI developments

- Chip init / configuration

- Linux kernel & basic BSP

- Optimized general purpose libraries (non-automotive specfic) incl. standard accelerator libraries

- General benchmarking

- General dev-environment and SDK, CI, Versioning ....

Take over from GPP, Accelerator or automotive specific accelerator team

Core team + EB

### **EPIFOR EXASCALE**

Copyright © European Processor Initiative 2019.

#### European Processor Initiative

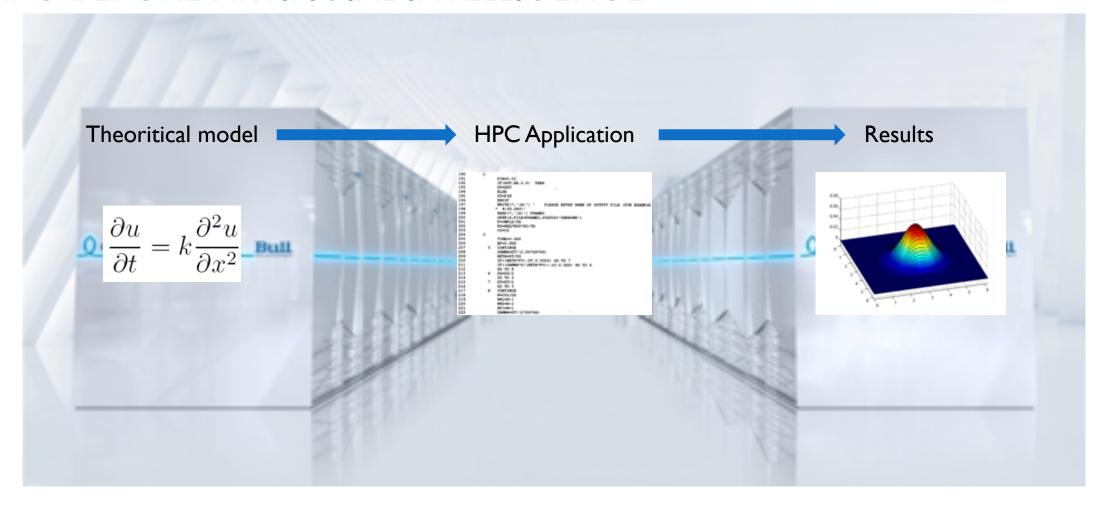

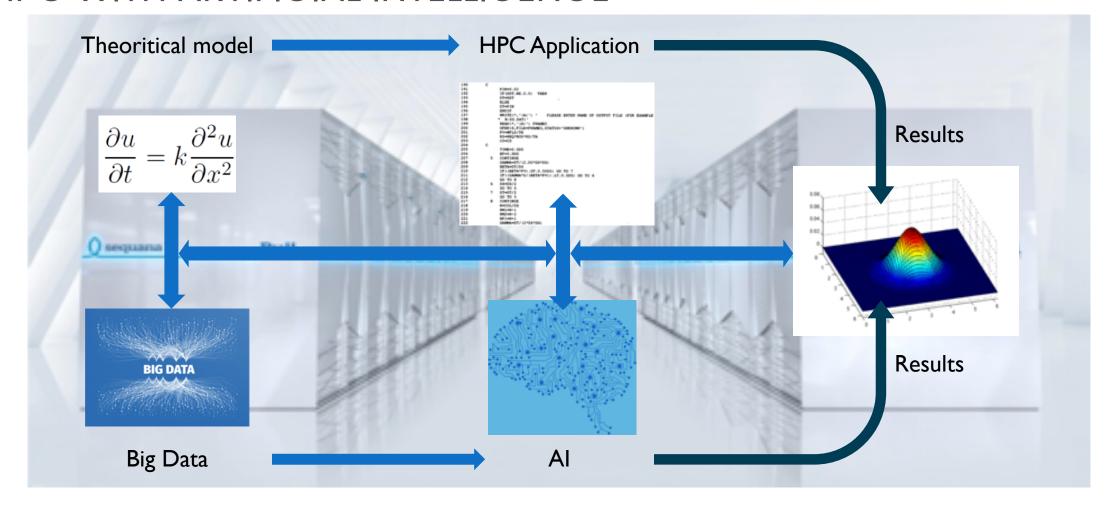

#### HPC BEFORE ARTIFICIAL INTELLIGENCE

#### European Processor Initiative

#### HPC WITH ARTIFICIAL INTELLIGENCE

Public Clouds

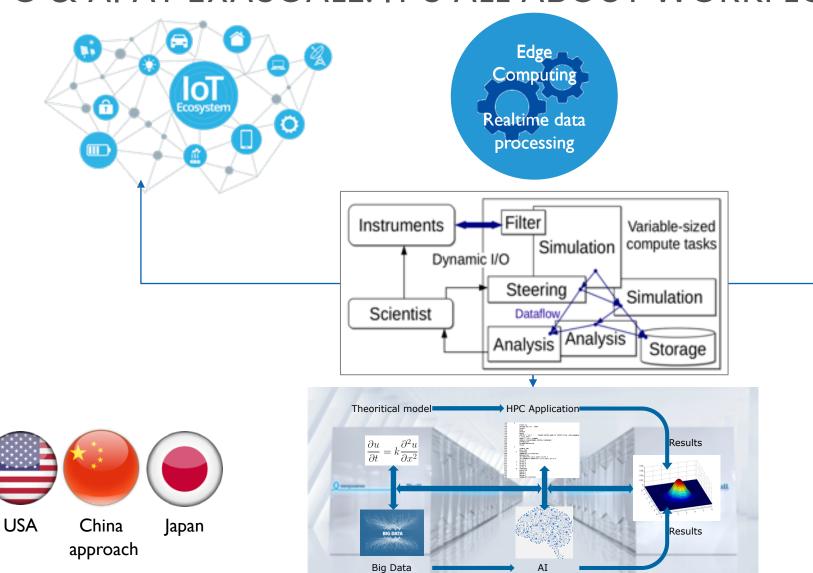

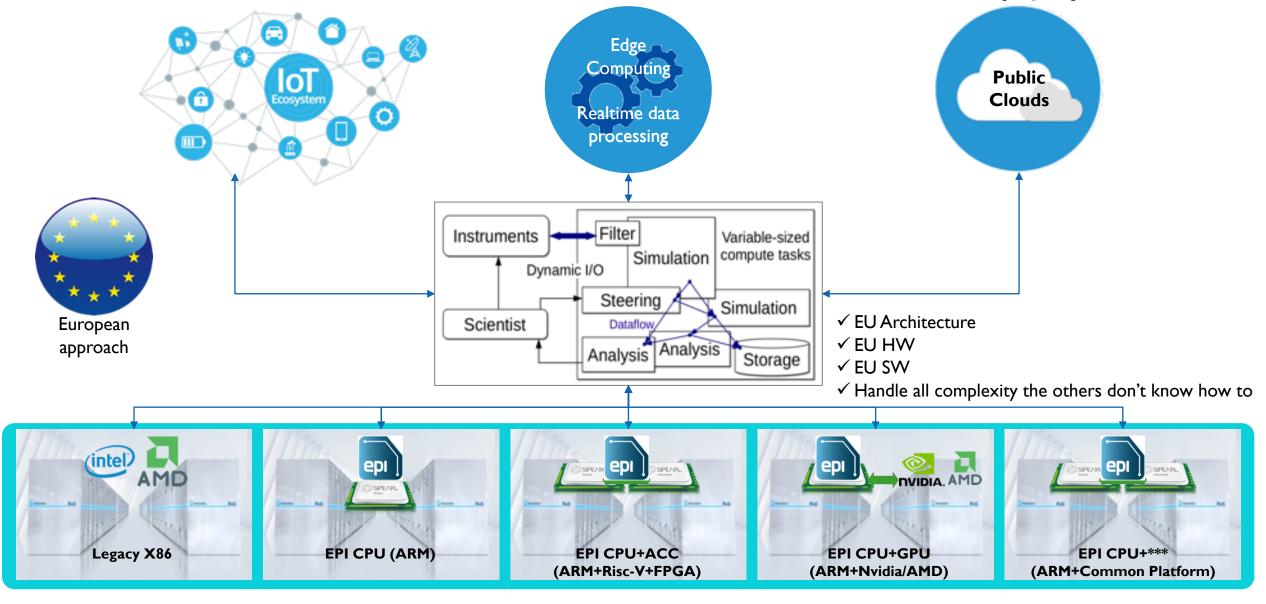

## HPC & AI AT EXASCALE: IT'S ALL ABOUT WORKFLOWS (1/2)

## HPC & AI AT EXASCALE: IT'S ALL ABOUT WORKFLOWS (2/2)

## CONCLUSION

#### EPI NEXT CHALLENGES

# Build on existing IP and w. communities

- Risk minimized by leveraging existing work

- Open Source, previous projects, external partners

- Future-proofed by favoring open standards & simpler programming models

- Legacy taken into account to widen the potential user-base

# Close the gap between R&I and industrial products

- Have EPI "delivery and product" oriented while fulfilling its needs for Research and Innovation

- We need to be ready for production end of 2021

- Face a WW class competition

- We will not be used because we are "engineered" in EU but because we have the best and cost effective solution

- Re-create a real ecosystem for deep node microelectronics:

- Engineers

- IP's

- ...factories...

### THANK YOU FOR YOUR ATTENTION

- www.european-processor-initiative.eu

- @EuProcessor

- in European Processor Initiative

- <u>European Processor Initiative</u>