# EPI TUTORIAL: FIRST STEPS TOWARDS A MADE-IN-EUROPE HIGHPERFORMANCE MICROPROCESSOR

CO-LOCATED WITH THE ACM 2019 SUMMER SCHOOL ON HPC ARCHITECTURES FOR AI AND DEDICATED APPLICATIONS

UNIVERSITAT POLITÈCNICA DE CATALUNYA, BARCELONA, SPAIN

17 JULY 2019

Association for

**Computing Machinery**

# FRAMEWORK PARTNERSHIP AGREEMENT IN EUROPEAN LOW-POWER MICROPROCESSOR TECHNOLOGIES

THIS PROJECT HAS RECEIVED FUNDING FROM THE EUROPEAN UNION'S HORIZON 2020 RESEARCH AND INNOVATION PROGRAMME UNDER GRANT AGREEMENT NO 826647

### **AGENDA**

| Start | Finish | Topic                                  | Presenter               |

|-------|--------|----------------------------------------|-------------------------|

| 14:00 | 14:25  | HPC processor landscape                | Andrea Bartolini, UNIBO |

|       |        | Main challenges for HPC processor      |                         |

|       |        | Architecture evolution towards         |                         |

|       |        | heterogeneity                          |                         |

|       |        | Semiconductor technology overview      |                         |

|       |        | European landscape and introduction to |                         |

|       |        | EuroHPC                                |                         |

| 14:25 |        | European Processor Initiative (EPI)    |                         |

| 14:25 | 14:35  | Overview                               | Andrea Bartolini, UNIBO |

| 14:35 | 14:50  | Processor and general architecture     | Andrea Bartolini, UNIBO |

| 14:50 | 15:00  | Co-design process and modeling         | Andrea Bartolini, UNIBO |

| 15:00 | 15:45  | Accelerator                            | Mauro Olivieri, BSC     |

| 15:45 | 16:30  | Software                               | Jesus Labarta, BSC      |

|       |        |                                        | Jaume Abella, BSC       |

| 16:30 | 17:00  | Automotive                             | Francisco Cazorla, BSC  |

|       | 17:00  | End                                    |                         |

Copyright © European Processor Initiative 2019. EPI Tutorial/Barcelona/17-07-2019

### **HPC PROCESSOR LANDSCAPE**

ANDREA BARTOLINI (SLIDES PREPARED BY DENIS DUTOIT)

### HPC PROCESSOR LANDSCAPE

| Start | Finish | Topic                                          | Presenter                      |

|-------|--------|------------------------------------------------|--------------------------------|

| 14:00 | 14:25  | HPC processor landscape                        | Andrea Bartolini, UNIBO        |

|       |        | Main challenges for HPC processor              | Slides Prepared (Denis Dutoit) |

|       |        | Architecture evolution towards heterogeneity   |                                |

|       |        | Semiconductor technology overview              |                                |

|       |        | European landscape and introduction to EuroHPC |                                |

### HIGH PERFORMANCE COMPUTING EVOLUTION

| • | Starting from high          |  |  |  |  |

|---|-----------------------------|--|--|--|--|

|   | performance compute only,   |  |  |  |  |

|   | <b>HPC</b> evolves towards: |  |  |  |  |

- New workloads

- Massive volume of data

| New drivers            | Requirements                                                                                                                | Solutions                                                         |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

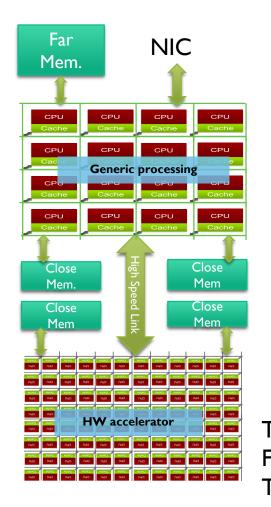

| New workloads          | More computing performance (Ops per second), also for simple operations (FP16, FP8, INT). Energy efficiency (Ops per Watt). | Heterogeneity: Generic processing + accelerators Low power design |

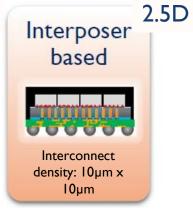

| Massive volume of data | Increased Bytes per Flops. High bandwidth/low latency access to all data.                                                   | High Bandwidth<br>Memories and 2.5D<br>integration                |

TERA 1000 - CEA

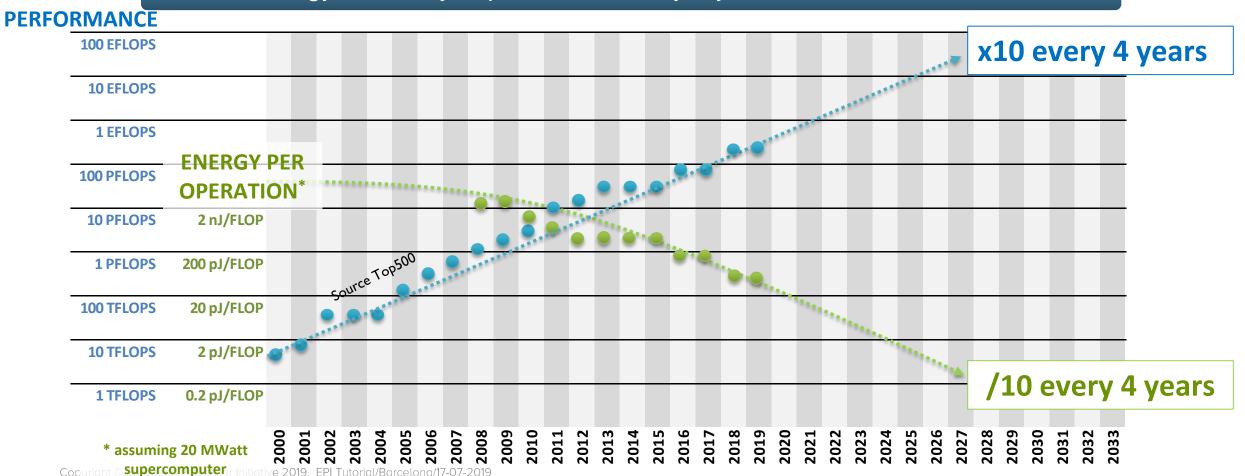

### CHALLENGES FOR ADVANCED COMPUTING

10x energy efficiency improvement every 4 years

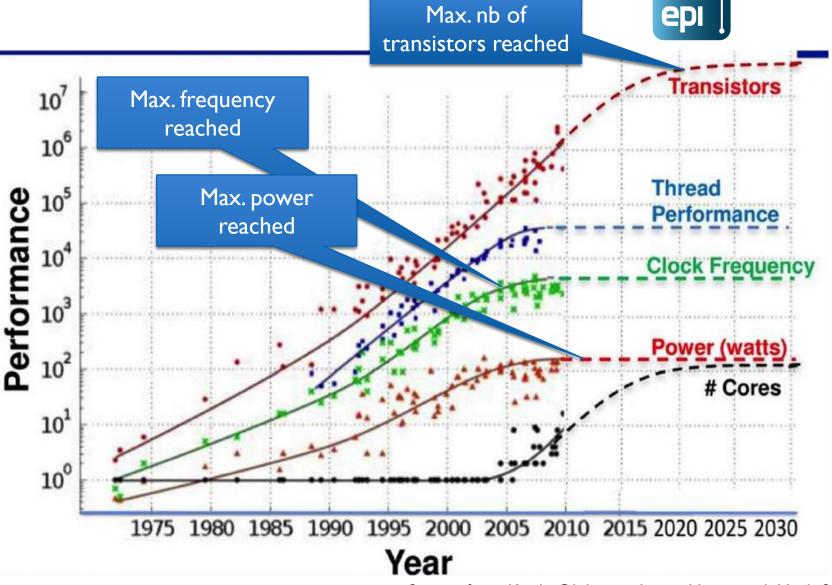

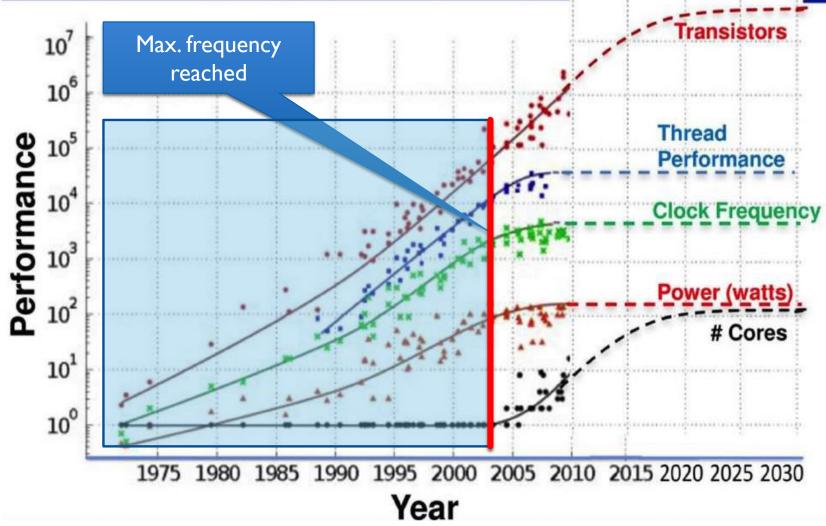

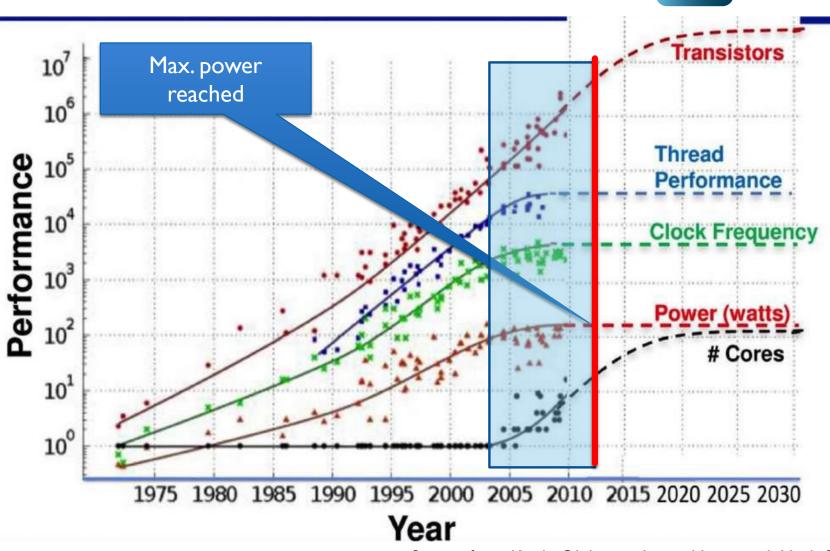

# TECHNOLOGY SCALING TRENDS

Source from Kunle Olukotun, Lance Hammond, Herb Sutter, Burton Smith, Chris Batten, and Krste Asanoviç

European Processor Initiative

### European Processor Initiative

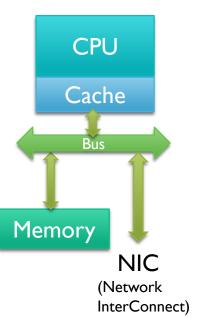

### HAPPY SCALING

Source from Kunle Olukotun, Lance Hammond, Herb Sutter, Burton Smith, Chris Batten, and Krste Asanovic

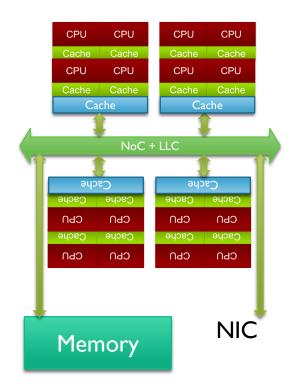

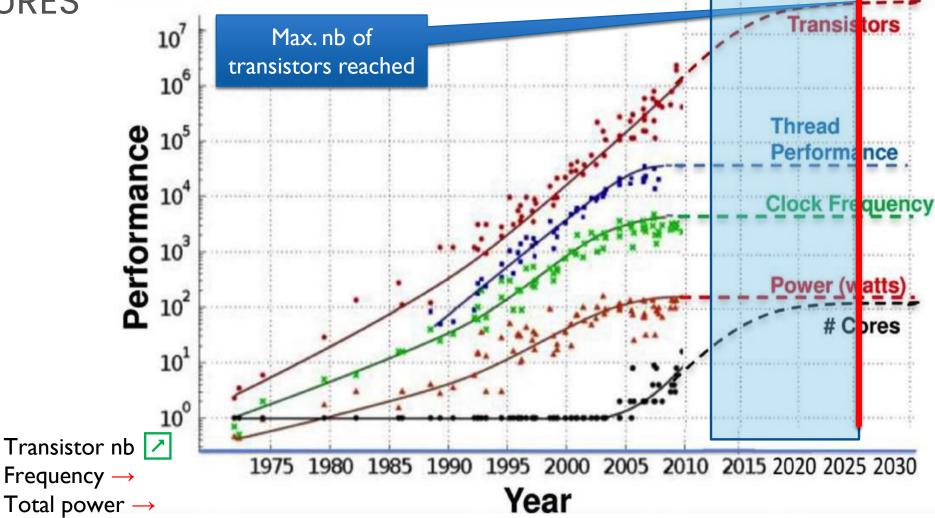

### MANY-CORES

Transistor nb

Frequency →

Power density →

Source from Kunle Olukotun, Lance Hammond, Herb Sutter, Burton Smith, Chris Batten, and Krste Asanovic

European Processor Initiative

epi

# HETEROGENEOUS ARCHITECTURES

Source from Kunle Olukotun, Lance Hammond, Herb Sutter, Burton Smith, Chris Batten, and Krste Asanovic

European Processor Initiative

epi

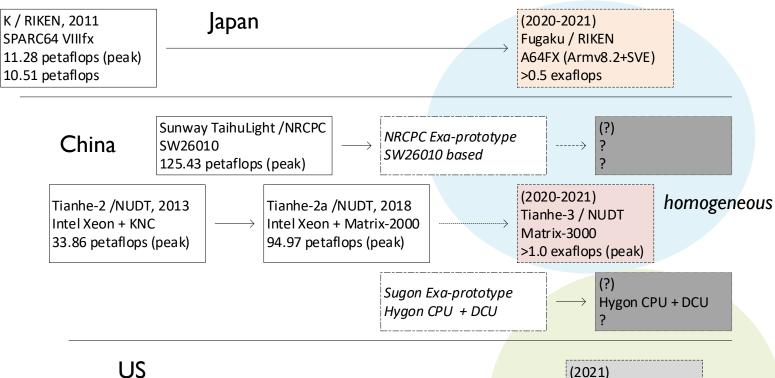

### RACE TO EXASCALE

- CPU architecture choice

- x86 + accelerator (heterogeneous)

- Arm/SVE (homogeneous)

- Others

EPI takes 2-step approach

step#I: homogeneous with Arm core+SVE

step#2: heterogeneous with additional EPI accelerators

Summit / ORNL, 2019 IBM P9 + NVidia GPU 200 petaflops (peak) 148.6 petaflops Sierra / LLNL, 2019

IBM P9 + NVidia GPU 125 petaflops (peak)

Aurora / ANL Intel Xeon + Xe >1.0 exaflops (peak)

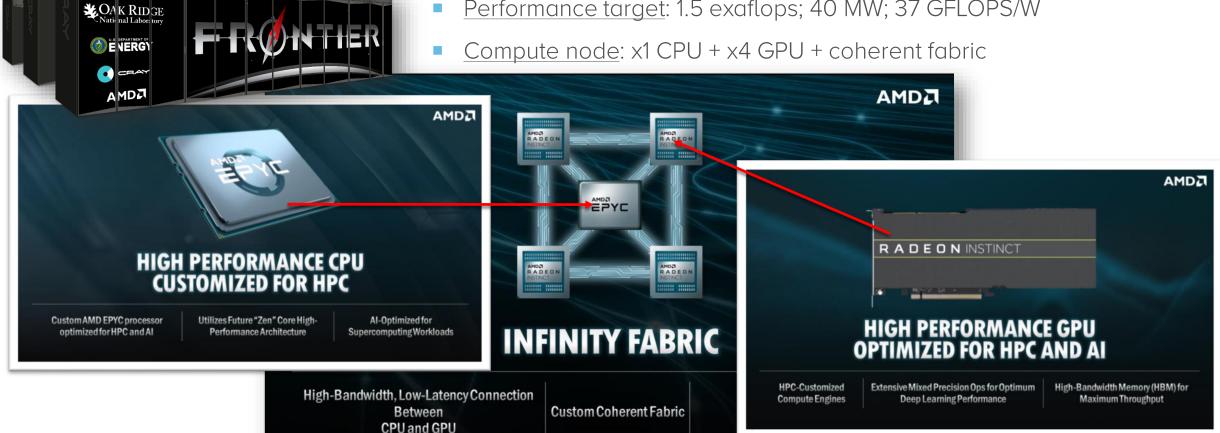

> (2021)Frontier / ORNL AMD CPU + GPU ~1.5 exaflops (peak)

heterogeneous, accelerated

### 53RD EDITION OF THE TOP500 LIST (JUNE, 2019)

Heterogeneous integration?

|     | Rank                  | Site                                                                | System                                                                                                                                             | Cores      | Rmax<br>(TFlop/s) | Rpeak<br>(TFlop/s) | Power<br>(kW) |

|-----|-----------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|--------------------|---------------|

| Yes | 1                     | DOE/SC/Oak Ridge National<br>Laboratory<br>United States            | Summit - IBM Power System<br>AC922, IBM POWER9 22C 3.07GHz,<br>NVIDIA Volta GV100, Dual-rail<br>Mellanox EDR Infiniband<br>IBM                     | 2,414,592  | 148,600.0         | 200,794.9          | 10,096        |

| Yes | 2                     | DOE/NNSA/LLNL<br>United States                                      | Sierra - IBM Power System<br>S922LC, IBM POWER9 22C 3.1GHz,<br>NVIDIA Volta GV100, Dual-rail<br>Mellanox EDR Infiniband<br>IBM / NVIDIA / Mellanox | 1,572,480  | 94,640.0          | 125,712.0          | 7,438         |

| No  | 3                     | National Supercomputing Center in<br>Wuxi<br>China                  | Sunway TaihuLight - Sunway MPP,<br>Sunway SW26010 260C 1.45GHz,<br>Sunway<br>NRCPC                                                                 | 10,649,600 | 93,014.6          | 125,435.9          | 15,371        |

| Yes | 4                     | National Super Computer Center in<br>Guangzhou<br>China             | <b>Tianhe-2A</b> - TH-IVB-FEP Cluster,<br>Intel Xeon E5-2692v2 12C 2.2GHz,<br>TH Express-2, Matrix-2000<br>NUDT                                    | 4,981,760  | 61,444.5          | 100,678.7          | 18,482        |

| Yes | <b>5</b><br>ona/17-07 | Texas Advanced Computing Center/Univ. of Texas United States 7-2019 | Frontera - Dell C6420, Xeon<br>Platinum 8280 28C 2.7GHz,<br>Mellanox InfiniBand HDR<br>Dell EMC                                                    | 448,448    | 23,516.4          | 38,745.9           |               |

Copyright © European Processor Initiative 2019. EPI Tutorial/Barcelona/

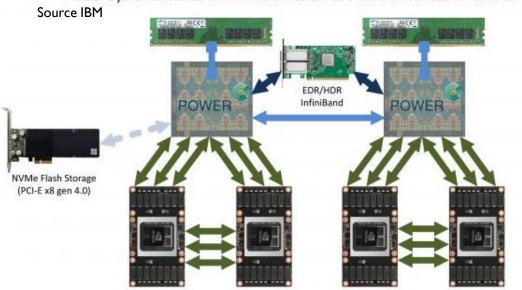

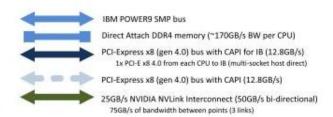

# TOP500 #1 & #2: NVIDIA TESLA V100 GPU + IBM POWER9 CPU

#### Server Block Diagram

Power Systems AC922 with NVIDIA Tesla V100 with Enhanced NVLink GPUs

#### NVIDIA TESLA V100 SPECIFICATIONS

Tesla V100 for NVLink

PERFORMANCE with NVIDIA GPU Boost\*\*

DOUBLE-PRECISION 7.8 teraFLOPS

SINGLE-PRECISION 15.7 teraFLOPS

DEEP LEARNING 125 teraFLOPS

INTERCONNECT BANDWIDTH Bi-Directional

NVLINK 300 GB/s

MEMORY CoWoS Stacked HBM2

CAPACITY

32/16 GB HBM2

BANDWIDTH

900 GB/S

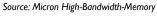

### AMD'S EPYC AND RADEON TO POWER **EXASCALE SUPERCOMPUTER**

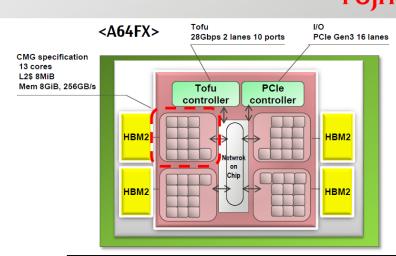

# GENERIC PROCESSING WITH SCALABLE VECTOR EXTENSION: FUJITSU & ARM

Source Fujitsu HotChips 2018

Generic processing is going towards ultra-high memory bandwidth

### **A64FX Chip Overview**

#### ■ Architecture Features

- Armv8.2-A (AArch64 only)

- SVE 512-bit wide SIMD

- 48 computing cores + 4 assistant cores\*

\*All the cores are identical

HBM2 32GiB

Tofu 6D Mesh/Torus

28Gbps x 2 lanes x 10 ports

PCIe Gen3 16 lanes

#### ■ 7nm FinFET

- 8,786M transistors

- 594 package signal pins

#### ■ Peak Performance (Efficiency)

- >2.7TFLOPS (>90%@DGEMM)

- Memory B/W 1024GB/s (>80%@Stream Triad)

|                  | A64FX<br>(Post-K) | SPARC64 XIfx<br>(PRIMEHPC FX100) |

|------------------|-------------------|----------------------------------|

| ISA (Base)       | Armv8.2-A         | SPARC-V9                         |

| ISA (Extension)  | SVE               | HPC-ACE2                         |

| Process Node     | 7nm               | 20nm                             |

| Peak Performance | >2.7TFLOPS        | 1.1TFLOPS                        |

| SIMD             | 512-bit           | 256-bit                          |

| # of Cores       | 48+4              | 32+2                             |

| Memory           | HBM2              | HMC                              |

| Memory Peak B/W  | 1024GB/s          | 240GB/s x2 (in/out)              |

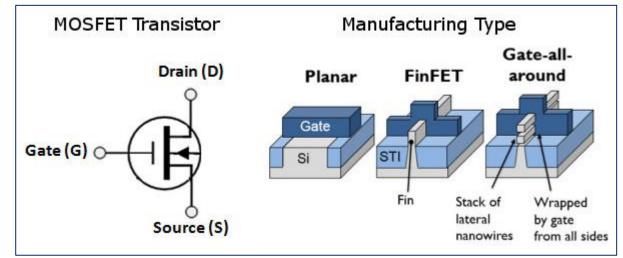

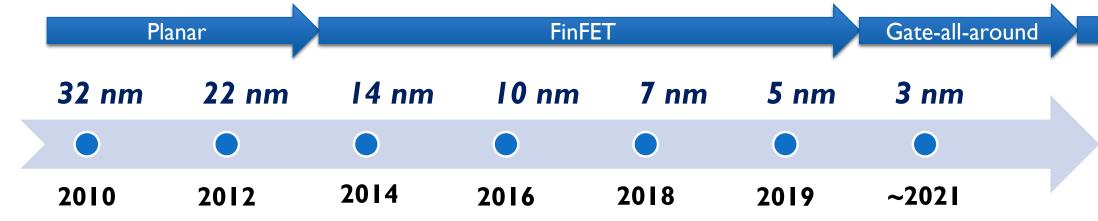

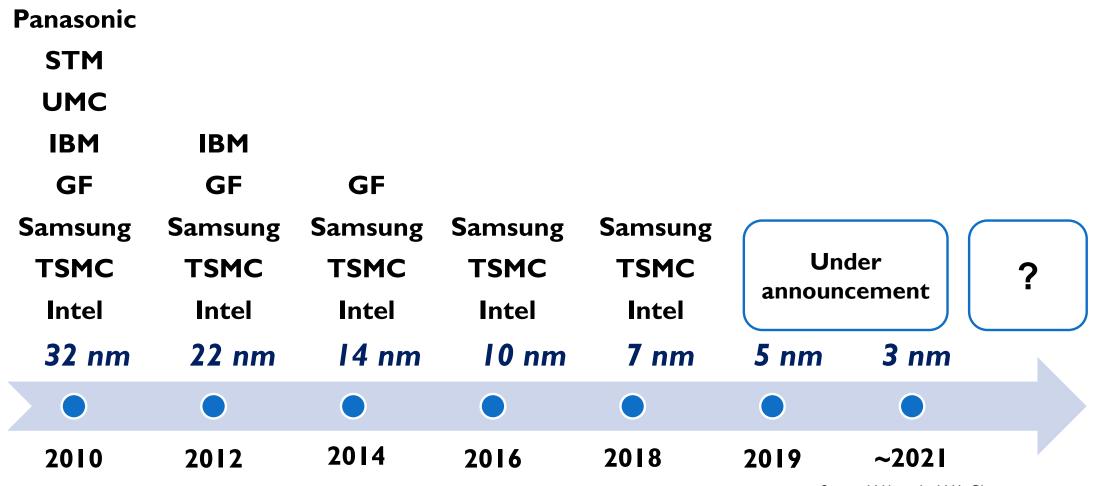

### SEMICONDUCTOR TECHNOLOGY EVOLUTION

Source ScienceDirect

Source Wikipedia, WikiChip

### European Processor Initiative

# SEMICONDUCTOR MANUFACTURING PROCESSES AND FOUNDRIES

Source Wikipedia, WikiChip

#### European Processor Initiative

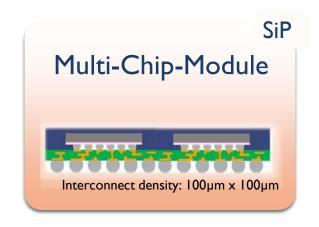

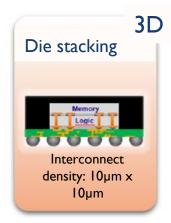

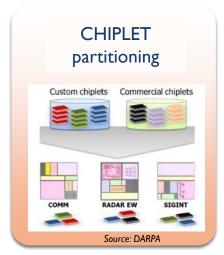

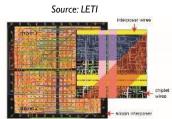

# FROM ADVANCED PACKAGING TECHNOLOGIES .... ... TO CHIPLETS

#### **Advanced Integration**

3D Integrated-Circuit (3D IC)

Source: GeorgiaTech

Copyright © European Processor Initiative 2019. EPI Tutorial/Barcelona/17-07-2019

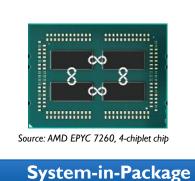

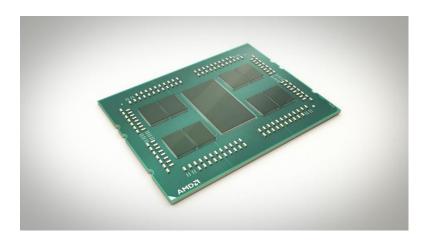

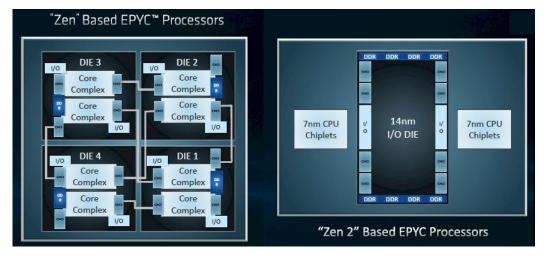

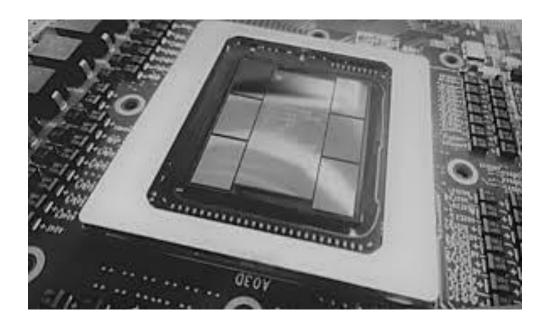

# MULTI-CHIP-MODULE: INTEGRATION WITH CHIPLETS

• AMD "Zen" architecture integrates upto 4 chiplets on a substrate; for scalable solution and more than reticle size silicon area in a chip.

(2017.10) EPYC 7260, 4-chiplet chip

AMD "Zen 2" architecture integrates upto 9 chiplets on a substrate

(2018.11) EPYC "Rome", 9-chiplet chip

(2018.11) AMD Zen2 architecture;

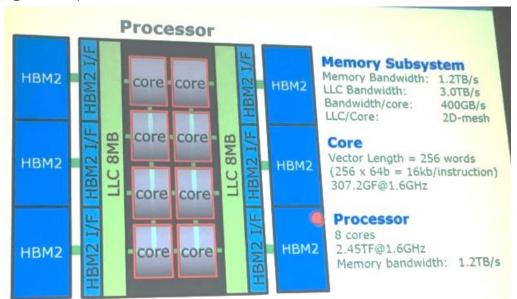

# 2.5D INTERPOSER: HBM INTEGRATION FOR MEMORY BANDWIDTH

- NEC Aurora SX-10+

- First product with 6x HBM2:

- 1.2 TB/s total memory bandwidth

- 2.45 TFLOPS

- ~0.5 Byte/Flops

### 53RD EDITION OF THE TOP500 LIST (JUNE 2019)

- Top#1 today:

- 0.2 10<sup>18</sup> Flop/s Peak

- It is 1/5 of Exascale level of performance

- Users:

#1-#2: US

#3-#4: China

Processor design & technology:

| Chip               | Design | Manuf. |

|--------------------|--------|--------|

| IBM POWER9         |        |        |

| NVIDIA Volta GVI00 |        | *      |

| Sunway SW26010     | *}     | *}     |

| Intel Xeon E5      |        |        |

| Rank | Site                                                     | System                                                                                                                                             |

|------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | DOE/SC/Oak Ridge National<br>Laboratory<br>United States | Summit - IBM Power System<br>AC922, IBM POWER9 22C 3.07GHz,<br>NVIDIA Volta GV100, Dual-rail<br>Mellanox EDR Infiniband<br>IBM                     |

| 2    | DOE/NNSA/LLNL<br>United States                           | Sierra - IBM Power System<br>S922LC, IBM POWER9 22C 3.1GHz,<br>NVIDIA Volta GV100, Dual-rail<br>Mellanox EDR Infiniband<br>IBM / NVIDIA / Mellanox |

| 3    | National Supercomputing Center in<br>Wuxi<br>China       | Sunway TaihuLight - Sunway MPP,<br>Sunway SW26010 260C 1.45GHz,<br>Sunway<br>NRCPC                                                                 |

| 4    | National Super Computer Center in<br>Guangzhou<br>China  | Tianhe-2A - TH-IVB-FEP Cluster,<br>Intel Xeon E5-2692v2 12C 2.2GHz,<br>TH Express-2, Matrix-2000<br>NUDT                                           |

### 53RD EDITION OF THE TOP500 LIST (JUNE 2019)

- Top#1 today:

- 0.2 10<sup>18</sup> Flop/s Peak

- It is 1/5 of Exascale level of performance

- Users:

#1-#2: US

#3-#4: China

Processor design & technology:

| Chip                 | Design | Manuf. |

|----------------------|--------|--------|

| IBM POWER9           |        |        |

| NVIDIA Volta GV I 00 |        | *      |

| Sunway SW26010       | *}     | *}     |

| Intel Xeon E5        |        |        |

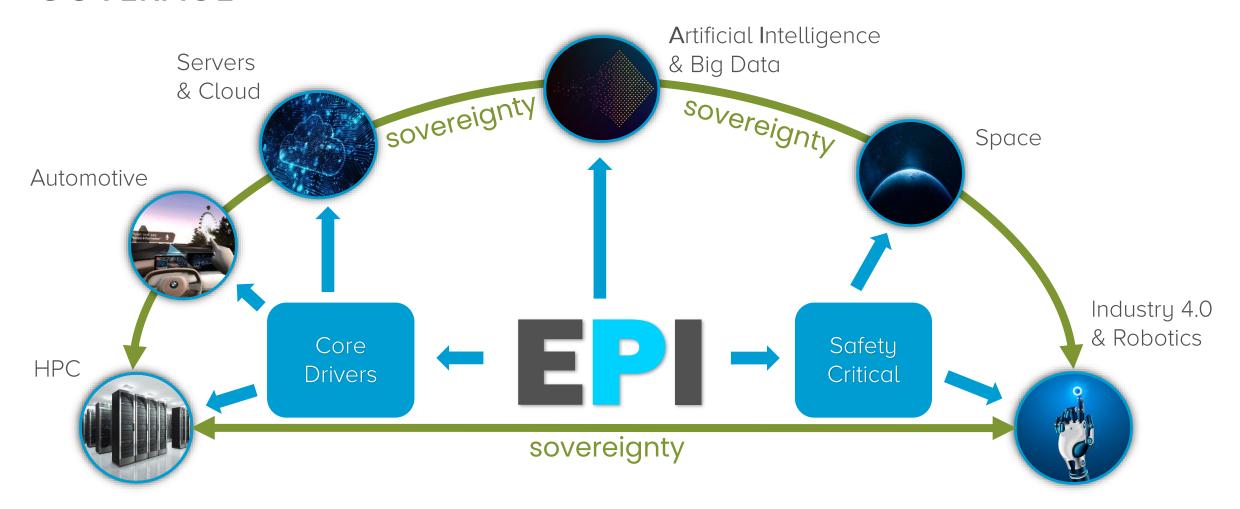

### WHY EUROPE NEEDS ITS OWN PROCESSORS

- Processors now control almost every aspect of our lives

- Security (back doors etc.)

- Possible future restrictions on exports to EU due to increasing protectionism

- A competitive EU supply chain for HPC technologies will create jobs and growth in Europe

- Sovereignty (data, economical, embargo)

NSA May Have Backdoors Built Into Intel And AMD Processors

A group of researchers showed how a Tesla Model \$600 worth of equipment

Car hacking remains a very real threat as autos become ever more loaded with tech

The US Cloud Act v The EU's GDPR - Data Privacy & Security

A jet sale to Egypt is being blocked by a US regulation, and France is over it

#### Image sources:

ps://www.theverge.com/2018/10/22/18011138/china-spy-chip-amazon-apple-super-micro-ceo-retraction

stolen-in-seconds-using-only-600-worth-of-equipment/articleshow/65761310

https://eu.freep.com/story/money/2018/01/13/car-hacking-threat/102827000

https://www.nearsetrust.ie/blog/the-us-cloud-act-v-the-eus-adpr-data-privacu-security

mtps://www.pearse-trustrie/biog/ine-us-croud-act-v-me-eus-gapi-aata-pii/vacy-security https://www.defensenews.com/global/europe/2018/08/01/a-jet-sale-to-egypt-is-being-blocked-by-a-us-

aulation-and-france-is-over-it/

### HOW EUROHPC WILL HELP TO MAKE US STRONGER

- Developing a new European supercomputing ecosystem: HPC systems, network, software, applications, access through the cloud

- Making HPC resources available to public and private users, including SMEs.

- Stimulating a technology supply industry

## EUROPEAN PROCESSOR INITIATIVE (EPI)

ANDREA BARTOLINI (SLIDES PREPARED BY DENIS DUTOIT)

### EUROPEAN PROCESSOR INITIATIVE (EPI)

| Start | Finish | Topic                               | Presenter               |

|-------|--------|-------------------------------------|-------------------------|

| 14:25 |        | European Processor Initiative (EPI) |                         |

| 14:25 | 14:35  | Overview                            | Andrea Bartolini, UNIBO |

| 14:35 | 14:50  | Processor and general architecture  | Andrea Bartolini, UNIBO |

| 14:50 | 15:00  | Co-design process and modeling      | Andrea Bartolini, UNIBO |

| 15:00 | 15:45  | Accelerator                         | Mauro Olivieri, BSC     |

| 15:45 | 16:30  | Software                            | Jesus Labarta, BSC      |

|       |        |                                     | Jaume Abella, BSC;      |

| 16:30 | 17:00  | Automotive                          | Francisco Cazorla, BSC  |

|       | 17:00  | End                                 |                         |

### **OVERVIEW**

ANDREA BARTOLINI (SLIDES PREPARED BY DENIS DUTOIT)

### EUROPEAN PROCESSOR INITIATIVE

- High Performance General Purpose Processor for HPC

- High-performance RISC-V based accelerator

- Computing platform for autonomous cars

- Will also target the AI, Big Data and other markets in order to be economically sustainable

www.european-processor-initiative.eu

#### **PROJECT PILLARS**

- Common platform and global architecture stream

- HPC general purpose processor stream

- Accelerator stream

- Automotive platform stream

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 826647

### **EPI OBJECTIVES**

- Architect of the <u>common platform</u> to accommodate the developed technologies

- CoDesign Methodology, Platform for hardware and software, Power management, Modeling and Simulation

- Build a <u>GPP processor chip</u> ready for PreExascale level machines (RheaR1)

- Develop <u>Accelerator technologies for HPC</u> workload (EPAC)

- Implementation of a <u>Real-time acceleration</u> PoC based on the first EPI GPP Processor (MPPA)

- Interfacing with the <u>Automotive MCU</u>

- Development efficient <u>power conversion</u> technologies

- Software activities based on the platform built

- PoC systems (test-chip; ref. board, HPC blades, PCIe card and automotive PoC)

- Related research around the EPI project scopes

### **EPI KPIS**

- Energy Efficiency

- \* Pre-ExaScale level with general-purpose CPU core in the first EPI GPP chip

- \* Develop acceleration technologies for better DP GFLOPS/Watt performance

- \* Inclusion of MPPA for real-time application acceleration

- \* Develop a Common Platform to enable EPI accelerations

- Easy to use

- \*Adopt Arm general-purpose CPU core with SVE / vector acceleration in the first EPI chip

- \* Supply sufficient Memory Bandwidth (Byte/FLOP) to support the GPP application

- \* in SGA1, focus on programming models to include accelerations.

### **EPI STREAMS**

SI - Common Stream

Codesign, Architecture, System software and key technologies for the Common Platform

S2 - GPP Processor

Design and implement of the processor chip(s) and PoC system

S3 - Acceleration

Foster acceleration technologies and create building blocks

S4 - Automotive

Address automotive market needs and create a pilot eHPC system

S5 - Administration

Manage and support activities

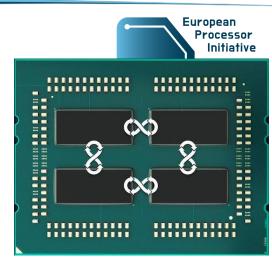

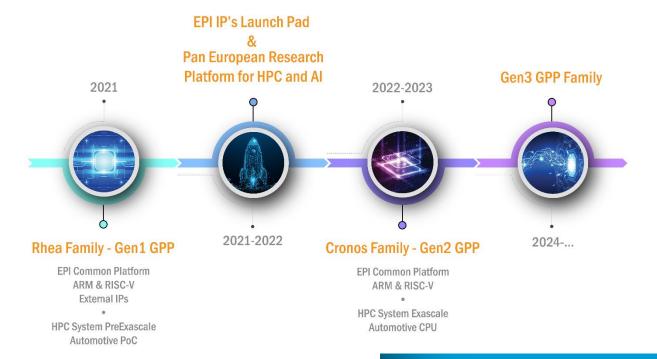

### GPP AND COMMON ARCHITECTURE

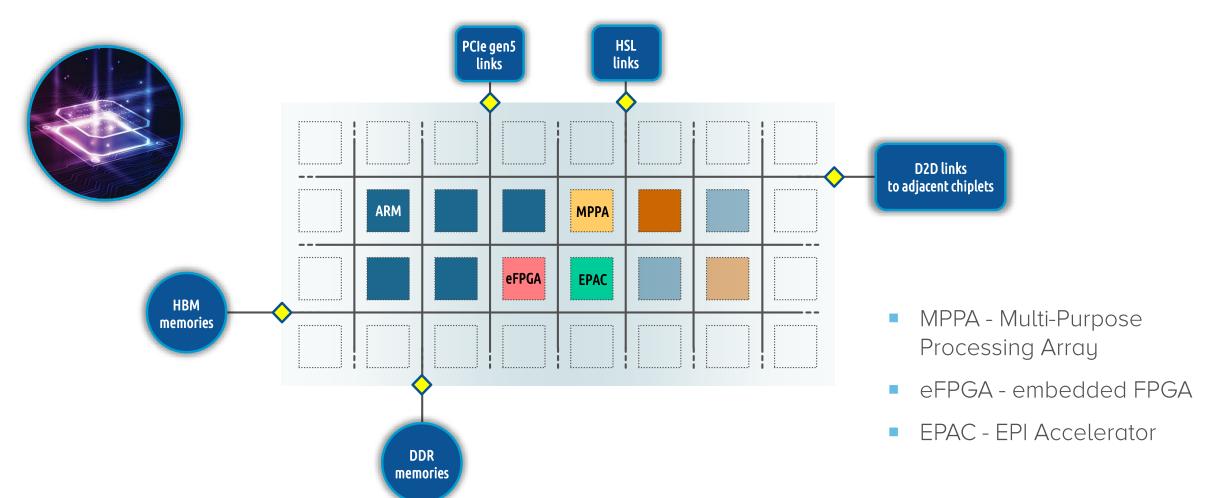

### EPAC - RISC-V ACCELERATOR

- EPAC EPI Accelerator

- VPU Vector Processing Unit

- STX Stencil/Tensor accelerator

- VRP VaRiable Precision co-processor

### **EPI AUTOMOTIVE**

- Autonomous driving systems

- Connected mobility

- EPI: A powerful data fusion platform the automotive embedded HPC platform

- EPI heterogeneous multicore architecture can provide enough performance and low power consumption in parallel

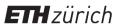

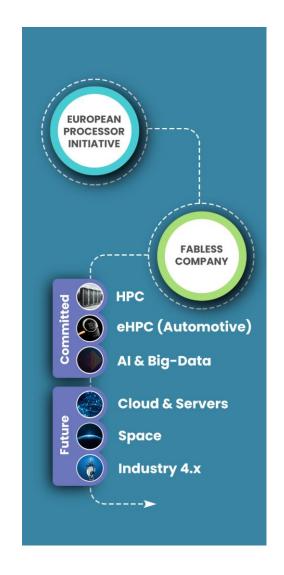

#### EPI FABLESS COMPANY

- EPI's Fabless company

- licence of IPs from the partners

- develop own IPs around it

- licence the missing components from the market

- generate revenue from both the HPC, IA, server and eHPC markets

- integrate, market, support & sales the chip

- work on the next generations

# SCALABILITY ALLOWS WIDE MARKET POTENTIAL COVERAGE

#### CONCLUSION

- HPC is crucial to resolve societal challenges and preserve European competitiveness

- Europe is going in the right direction with EuroHPC. This must be sustained in the long-term

- The chip design effort must continue for the EU's security and competitiveness, and should create a processor ecosystem covering IoT, servers, cloud, autonomous connected vehicles and HPC

- w www.european-processor-initiative.eu

- @EuProcessor

- in European Processor Initiative

- European Processor Initiative

## PROCESSOR AND GENERAL ARCHITECTURE

DENIS DUTOIT - YINGCHIH YANG - ANDREA BARTOLINI - PATRICE HAMEAU

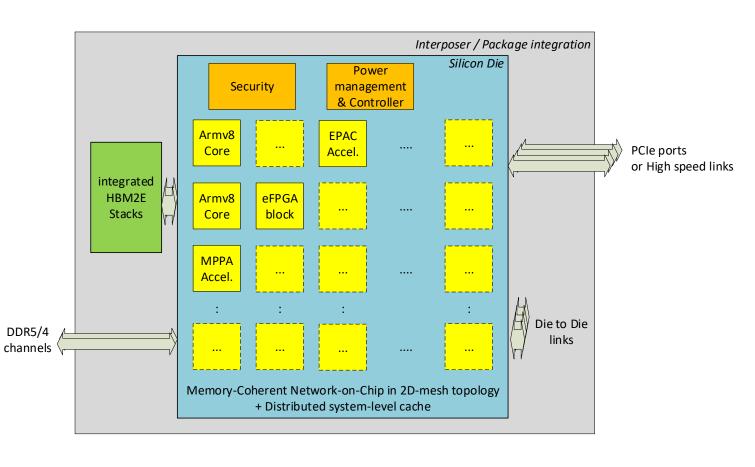

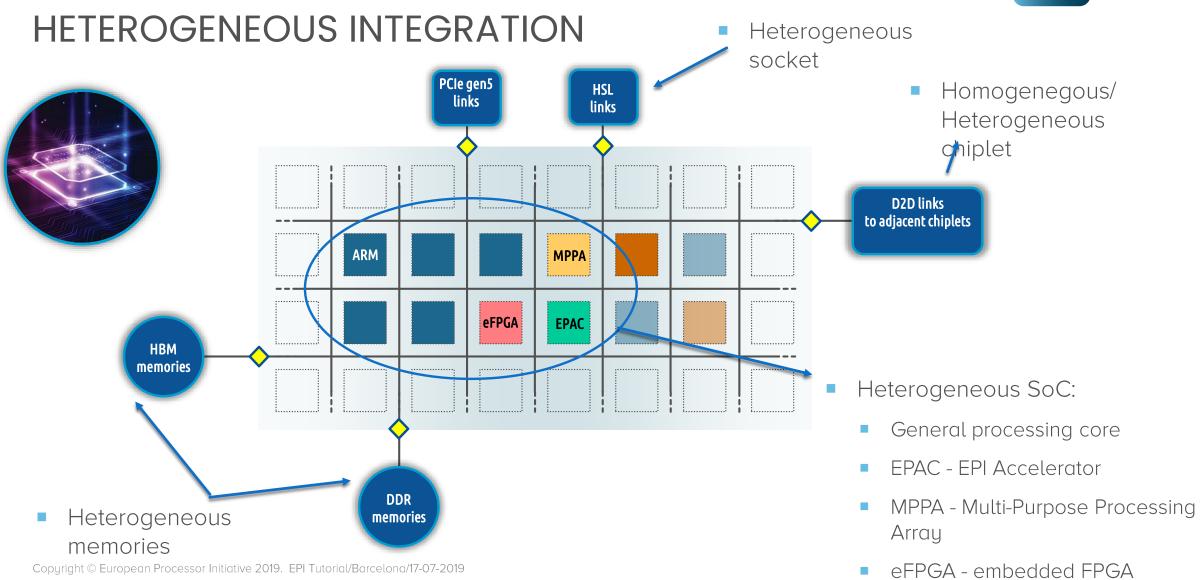

#### GENERAL ARCHITECTURE

- Memory-coherent NoC connects

- Array of computing units (CU)

- Memory and I/O controllers

- Bridge to links

- High speed links

- D2D links to connect on-package dies

- HSL links to connect on-board packages

- Top level infrastructures

- Power management & controller

- Security

NoC: network on chip

HSL: High speed links (with memory coherent support)

## GENERAL ARCHITECTURE (#2)

- Interfaces to connect acceleration functions to the NoC

- Data access and sharing throught AXI ports

- Receiving interrupt

- Power management

- Enable memory-centric computations

- Same copy of dataset is shared by multiple CUs

- In the ext. memory (DDR or HBM) cached by SLC cache

- In the local scratch memories near or local the acceleration blocks

- System MMU to provide same virtual memory view

**Power Management** Acceleration block infrastructure #1 Interrupt network AXI slave port AXI master port Acceleration Armv8 CPU Acceleration core with SVE block #1 block #2 dataset shared by NoC with SLC cache acceleration blocks dataset shared in memory ext. Memory

(HBM or DDR)

CU: Computing Unit; either Armv8 core with SVE or the EPAC/MPPA acceleration blocks SLC: System Level Cache; a last-level cache before ext. memories

Copyright © European Processor Initiative 2019.

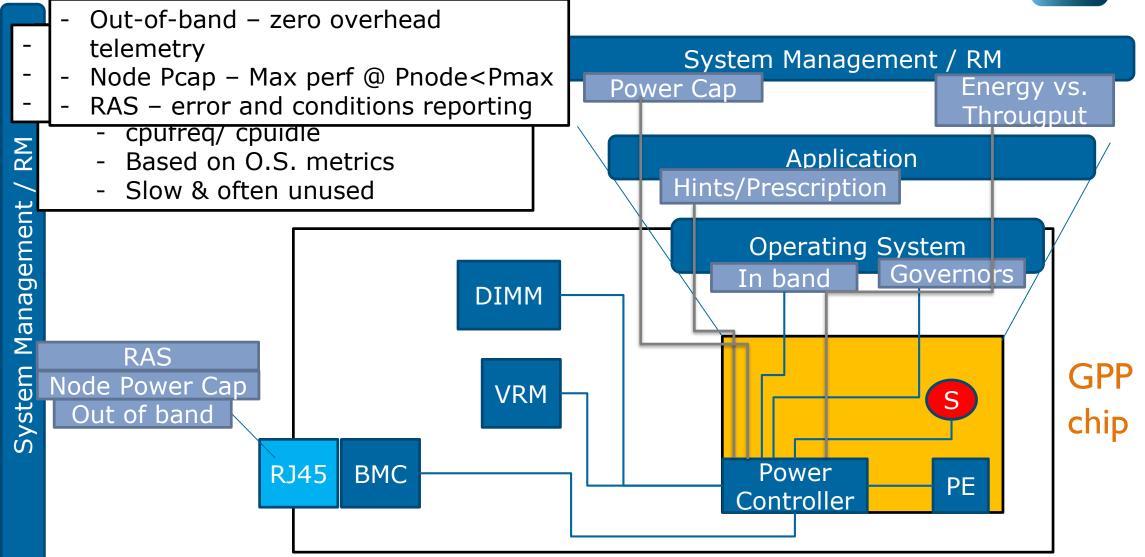

#### WP3 - POWER MANAGEMENT & CONTROLLER

Copyright © European Processor Initiative 2019. EPI Tutorial/Barcelona/17-07-2019

## POWER MANAGEMENT SOA & REQUIREMENTS

|                                                                                               | Intel         | IBM                | ARM          | AMD           | Cray          | Fujitsu         |  |

|-----------------------------------------------------------------------------------------------|---------------|--------------------|--------------|---------------|---------------|-----------------|--|

| Monitor                                                                                       | S, M, A, T    | N, S, M, A, T, U   | S, M, T      | N, S, M, A, T | N, S, M, A, N | N, S, C, M      |  |

| (Domain,Gra                                                                                   | 1ms           | <b>500us</b> ,10ms | 1-10KHz with | 1 sec (C),    | OOB           | <b>1ms</b> (N), |  |

| nularity)                                                                                     |               | aggregation        | SCP          | 1ms (G)       | (100ms)       | ~ns - model     |  |

|                                                                                               |               | 16ms for T &       |              |               |               | based (C)       |  |

|                                                                                               |               | U, 100ms           |              |               |               |                 |  |

|                                                                                               |               | aggregation        |              |               |               |                 |  |

| Control                                                                                       | S, M          | N, S, M, A         | S, M         | N, S, M, A    | N, S, M, A    | S, C, M,        |  |

| (Domain, Gra                                                                                  | RAPL 1ms      | 10-100ms           | 1-10KHz      | ~secs         | DVFS, RAPL,   | DVFS,           |  |

| nularity)                                                                                     | (in-band),    |                    | (100ms to    |               | min-max       | Decode          |  |

|                                                                                               | DVFS 500us    |                    | 1s)          |               | range, 10-    | Width,          |  |

|                                                                                               |               |                    |              |               | 30s at job    | HBM2 B/W        |  |

|                                                                                               |               |                    |              |               | launch        |                 |  |

| Interfaces,                                                                                   | RAPL MSRS,    | OpenBMC,           | ACPI, SCP    | Likwid,       | CapMC,        | Power API,      |  |

| Tools, etc                                                                                    | msr-safe,     | amester,           | (sys ctrl    | PAPI,         | PAPI, Cray    | PAPI            |  |

|                                                                                               | libmsr, PAPI, | <b>Memory Map</b>  | proc), IPA   | Memory        | ВМС           |                 |  |

|                                                                                               | likwid        |                    | (intelligent | Мар           | interfaces    |                 |  |

|                                                                                               | 6 5           | 6. 1.10            | allocator),  |               |               |                 |  |

|                                                                                               | Source Pov    | verStack I 9       | PAPI         |               |               |                 |  |

| Socket (S), Core (C), Memory (M), Accelerator (G), Node (N), Utilization (U), Temperature (T) |               |                    |              |               |               |                 |  |

EPI power management design is powered UNIBO and targets:

- Support for fine grain power monitoring, and control

- An higher performance power controller capable of supporting advanced power control algorithms.

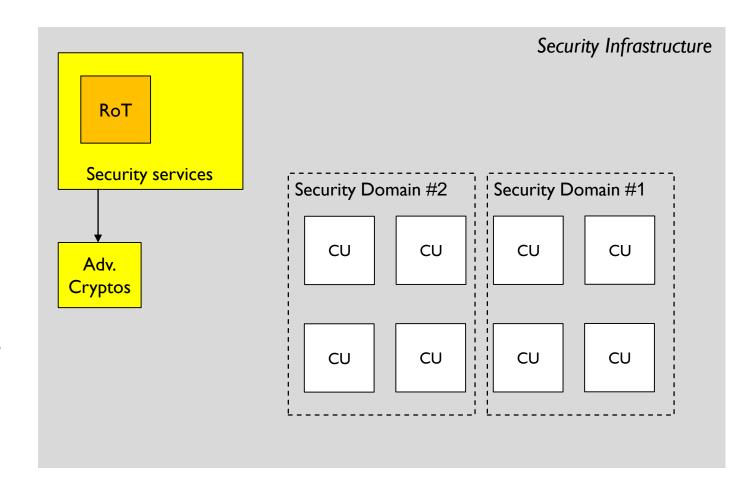

## SECURITY REQUIREMENTS

- Security aspects taken into account since the start of architecture definition:

- Strong Root of Trust (EAL4+ embedded Secure Element) always active during all chip lifecycle.

- Global security policy and chip monitoring can be managed independently of applications.

- Modular security levels to adapt to different applicative needs.

- Level can be raised to be compatible with automotive needs for security (including safety constraints)

- Future proof considerations for cryptographic assets (including post-quantic)

- Core security services made available to applications through API (mailbox) to ease independent and quick security update.

#### SECURITY IN EPI PROCESSOR

- Root of trust

- Secure Boot

- Security domains

- Security services isolated

- Advanced cryptographic functions

- Various monitors for fault-injection, physical intrusion and other conditions

## CO-DESIGN PROCESS AND MODELING

DENIS DUTOIT - ESTELA SUAREZ - NICOLAS VENTROUX

#### **EPI CO-DESIGN**

Architects within Streams

Requirements

**Benchmarks**

+

Model and Modeling

Simulator, Eval. requirements

Eval. results

**Application Experts**

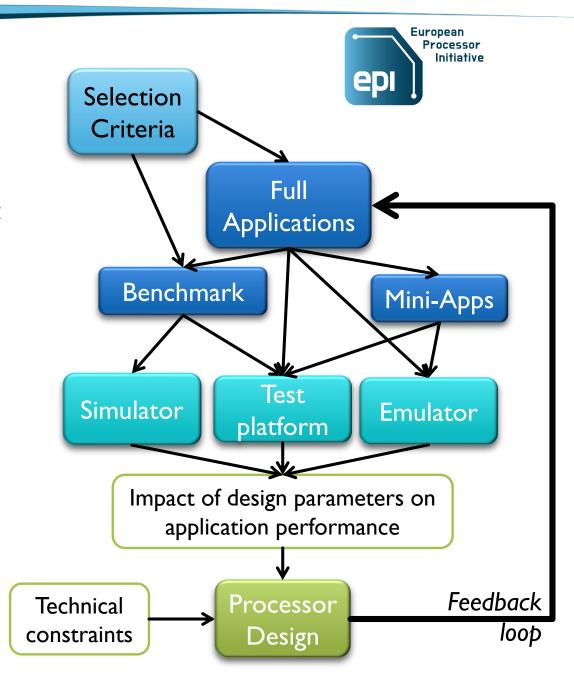

#### CO-DESIGN PROCESS

- Bi-directional and iterative interaction process between:

- application experts and

- hardware (HW) and system-software (SW) developers

- Multi-level suite of benchmarks

- from very low-level synthetic benchmarks to high-level applications

- Methodology with multi-level models & simulators

- 1). analytical models, high level

- 2). simulation based (e.g. gem5 simulation engine)

- 3). reference platform (e.g. Marvell ThunderX2)

- Node-level co-design parameters (e.g.):

- GPP: SVE length, number of SVE pipelines per core

- Accel.: vector registers length, ratio accelerator-vs-GPP cores

- Memory (size and BW): Cache, HBM, DDR

#### **APPLICATION SELECTION**

#### European Processor Initiative

#### Selection Criteria

| C1  | Relevant (now or in 5-years) markets                                                          |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------|--|--|--|--|

| C2  | Its requirements covers architectural components                                              |  |  |  |  |

| C3  | Represent a family/class of applications                                                      |  |  |  |  |

| C4  | Close relation to code developers                                                             |  |  |  |  |

| C5  | Licence allows development of mini-apps/derived benchmarks (preferable OpenSource)            |  |  |  |  |

| C6  | Reference data available from other platforms                                                 |  |  |  |  |

| C7  | Application uses/covers a software component/<br>programming model relevant for an EPI market |  |  |  |  |

| C8  | Application features relatively simple kernel                                                 |  |  |  |  |

| C9  | High societal impact                                                                          |  |  |  |  |

| C10 | Part of an existing benchmark suite, or widely known                                          |  |  |  |  |

| C11 | Mini-app or kernels already available                                                         |  |  |  |  |

### Application Fields

- Biophysics

- Biology/Medicine

- Earth Sciences/Climate

- HEP & Fusion

- Material Sciences

- CFD

- Hydrodynamics

- PDE

- Image / Media

Automotive

HPDA

- Cryptography

- Machine Learning

- Deep learning

- Cloud

- Data Base

- Reference benchmarks (HPL, HPCG, Stream, DGEMM...)

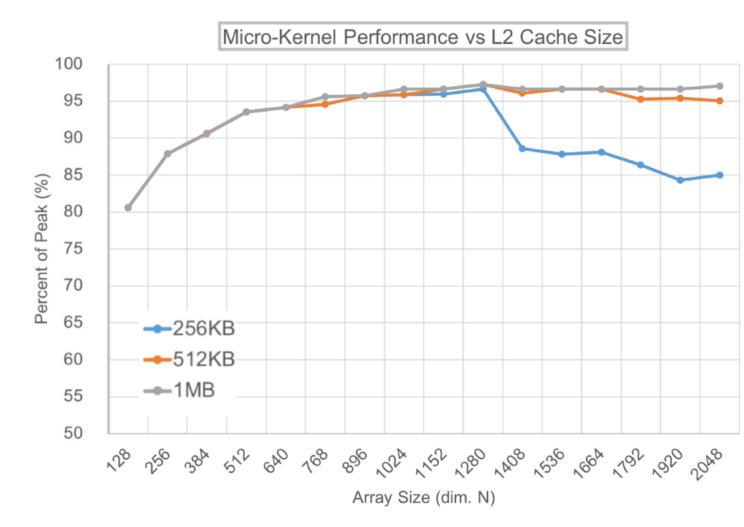

#### **EXAMPLE: DGEMM**

L2 cache exploration with BLIS microkernel

#### **CREDITS:**

- -P.Petrakis, V. Papaefstathiou et al. (FORTH): simulation execution an analysis

- -B.Brank, S.Nassyr (FZJ): BLIS micro-kernel

- -A.Portero (FZJ): Gem5 simulator setup

- Why simulation tasks in EPI?

- To make available high-level simulation tools to partners during the project

- Develop advanced innovative solutions for simulation

- Two technologies will be tuned for the EPI

- Early stage DSE with MUSA simulation (BSC)

- Early-stage performance prediction

- Trace-based simulators

- Virtual prototypes design with SESAM (CEA)

- Fast and parallel High-level SystemC/TLM simulation of manycore chips

- DSE and early SW development and validation

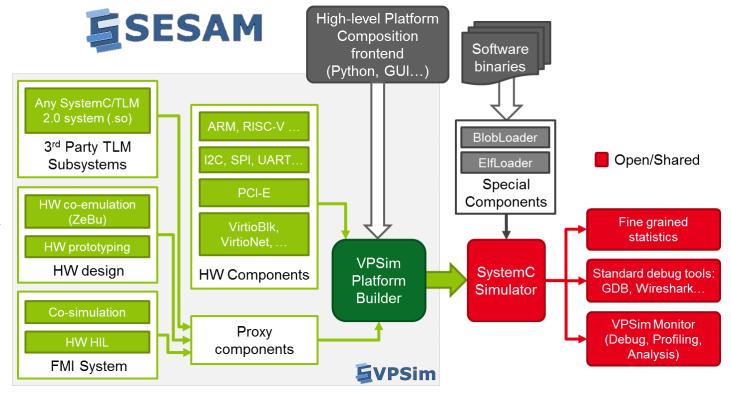

## SESAM/VPSIM

- Virtual prototyping framework

- Large and flexible IP portfolio

- Supports models from native library & ext. providers (QEMU 3.1, ARM Fast Models, NoCs...)

- SystemC / TLM 2.0 simulations

- Co-simulation & co-emulation for RTL valid.

- Co-simulation with 3rd-party tools (FMI standard)

- Designed to run full software stacks

- Firmware, bootloader, hypervisor, OS kernel, user applications

- Develop, debug, profile using std. tools

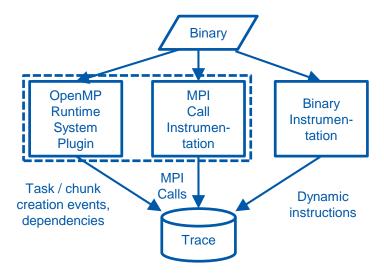

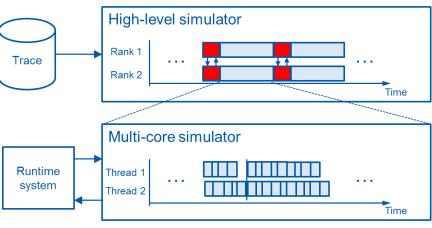

#### **MUSA**

- Usage/objectives

- Combine detailed trace driven simulation with sampling strategies

- Exploration of HPC architectural parameters affecting performance at scale

- A multi-level approach

- First level: trace generation

- OpenMP runtime system plugin

- MPI call instrumentation

- Pintool / DynamoRIO

- Second level: simulation

- A network simulator plays the obtained traces

- Multi-core detailed simulation of a set of computation phases

- Extrapolation of results for large scale HPC

- Support different modes

- Burst, detailed, sampling) trading accuracy for speed