Barcelona Supercomputing Center Centro Nacional de Supercomputación

EPI and beyond: perspectives of a European supercomputing center on open-source hardware and software

Mauro Olivieri visiting researcher, BSC professor, Sapienza Univ. of Rome

06/2019

### **Barcelona Supercomputing Center Centro Nacional de Supercomputación**

#### **BSC-CNS objectives**

Life, Earth and **Engineering Sciences**  Technology Transfer, public engagement

| BSC-CNS is                    | Spanish Government                   | 60% |

|-------------------------------|--------------------------------------|-----|

| a consortium<br>that includes | Catalan Government                   | 30% |

| that includes                 | Univ. Politècnica de Catalunya (UPC) | 10% |

**EU** researchers

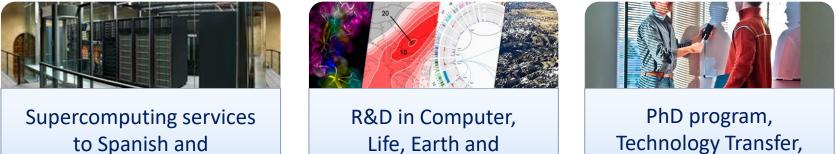

### **People evolution**

#### BSC Staff 2005 - 2018

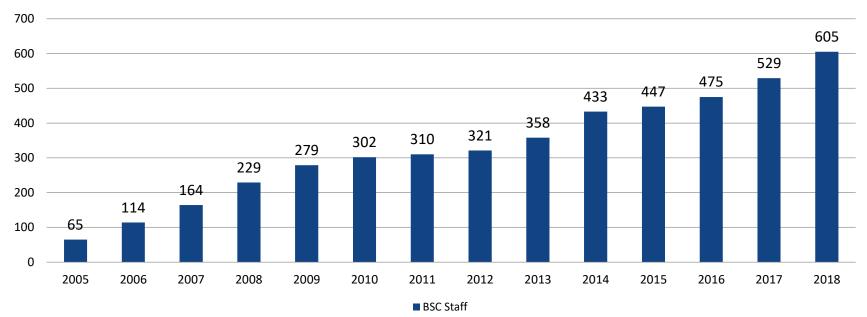

### **BSC & The Global IT Industry 2018**

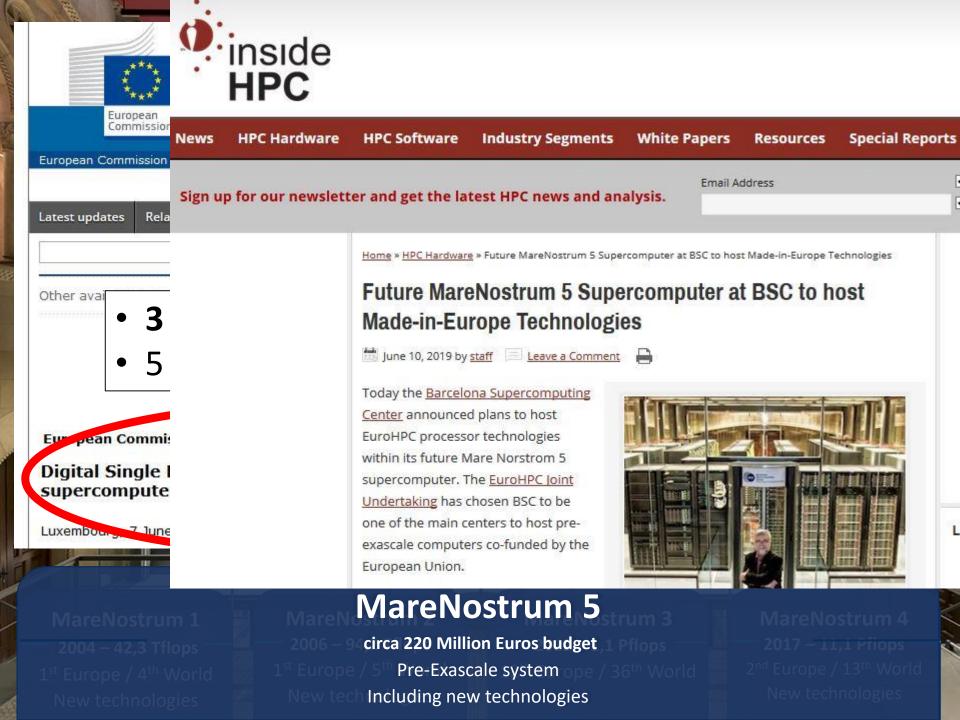

# Why is HPC Needed?

- Will save billions by helping us to adapt to climate change

- Will improve human health by enabling personalized medicine

- Will improve fuel efficiency of aircraft & help design better wind turbines

- Will help us to understand how the human brain works

Images courtesy of The PRACE Scientific Steering Committee, "The Scientific Case for Computing in Europe 2018-2026"

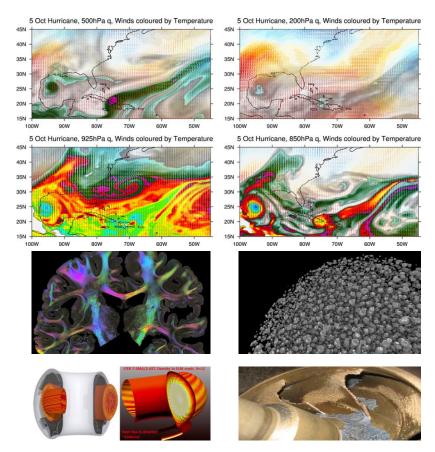

# The roadmap towards Exascale

# Where Europe needs to be stronger

- Only 1 of the 10 most powerful HPC systems is in the EU

- HPC codes must be upgraded

- Vital HPC hardware elements are missing: General Purpose Processor and Accelerators

EU needs its own source of as many of the system elements as possible

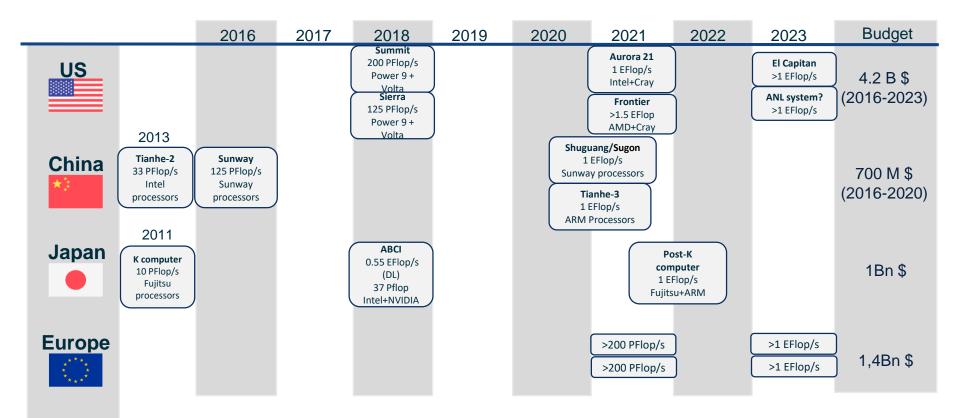

# Why Europe needs its own Processors

- Processors now control almost every aspect of people's lives

- Security (back doors etc.)

- Possible future restrictions on exports to EU due to increasing protectionism

- A competitive EU supply chain for HPC technologies will create jobs and growth in Europe

Images courtesy of Reuters.com and European Processor Initiative

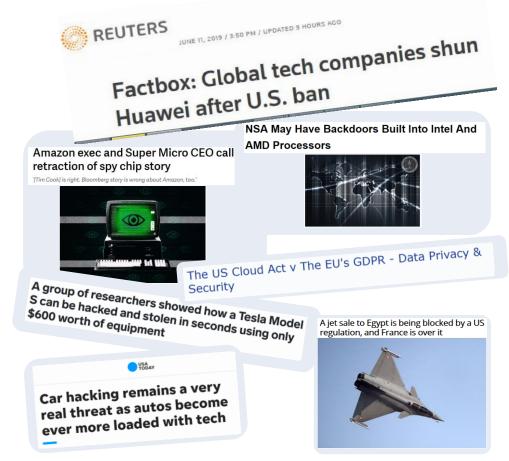

### The new European framework

#### Horizon Europe The EU's next research and innovation programme (2021 – 2027)

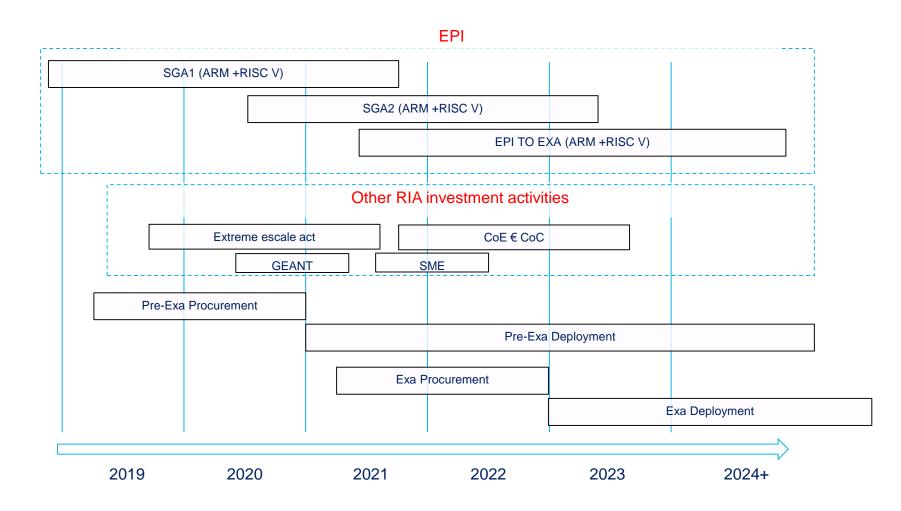

# **EuroHPC Roadmap**

# **EPI roadmap**

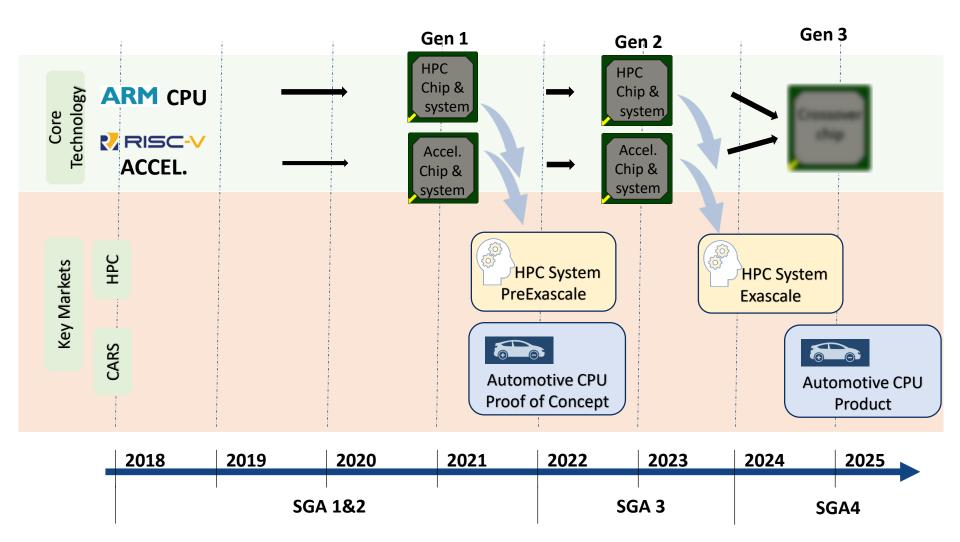

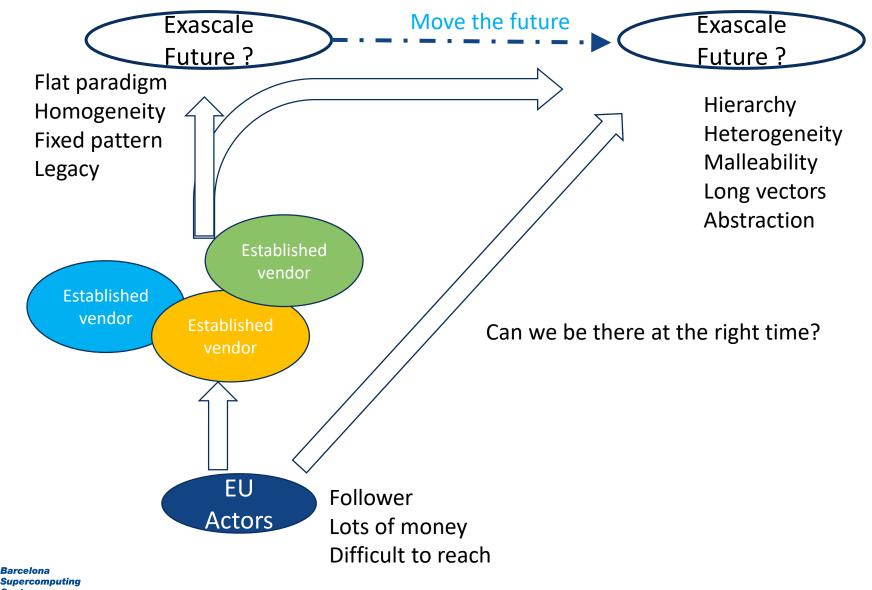

# BSC's exascale vision in EPI (and beyond)

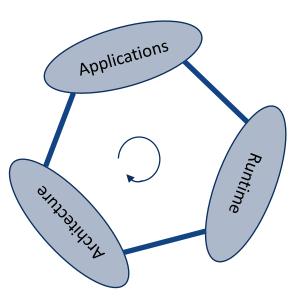

- Ensure programmers survive the "exascale" future

- Can we "move the future" ?

- Maximize take-up  $\rightarrow$  standards

- Co-design

- Issues addressed in multiple places

- Runtime aware architectures

- Runtime provides total abstraction

# More about the vision

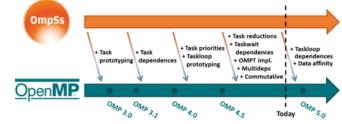

# **BSC's vision in EPI RISC-V vector processor**

- Low power: relatively low voltage , relatively low frequency

- High throughput devices

- Long Vectors

- Optimize memory throughput (High BW, B/F), locality

- Decoupled architecture

- ISA is important:

- "limited" number of control flows

- Hierarchical Acceleration

- Nested hierarchical parallelism

- Balanced hierarchy

- Homogenized heterogeneity

#### MPI+OpenMP paradigm

- Throughput oriented programming approach

- Malleability in application + Dynamic resource (cores, power, BW) management

- Intelligent runtimes & Runtime Aware Architectures

- Handle overlap and locality

- Reduce overhead  $\rightarrow$  hierarchical

- Architectural support for the runtime

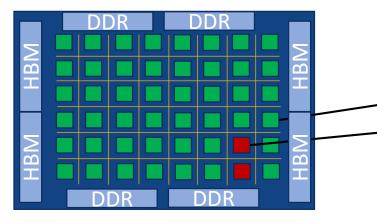

# **EPI chips**

#### General Purpose Processor (GPP) chip

- 7 nm, chip-let technology

- ARM-SVE tiles

- RISC-V vector+Al accelerator tiles

- L1, L2, L3 cache subsystem + HBM + DDR

**RISC-V** Accelerator Demonstrator **Test Chip**

- 22 nm FDSOI

- Only one RISC-V accelerator tile

- On-chip L1, L2 + off-chip HBM + DDR PHY

- Targets 128 DP GFLOPS (vector proc.)

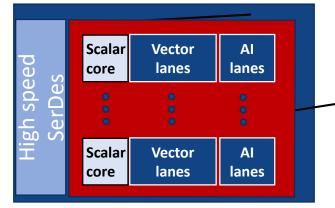

# The "killer mobile processors"...

( Microprocessors killed the Vector supercomputers

- ( They were not faster ...

- I ... but they were significantly cheaper and greener

Barcelona

#### Supercomputing Center Centro Nacional de Supercomputación

- ( History may be about to repeat itself ...

- ( Mobile processor are not faster ...

- Image: Image:

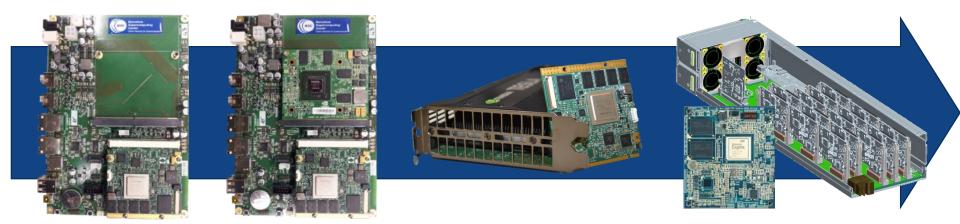

# ARM-based prototypes at BSC

**2011** Tibidabo **2012** KAYLA

**2013** Pedraforca **2014** Mont-Blanc

ARM multicore

ARM + GPU CUDA on ARM ARM + GPU Inifinband RDMA

Single chip ARM+GPU OpenCL on ARM GPU

# **The Open-Source Hardware Opportunity**

- In 2015, Mateo Valero said he believed a European Supercomputer based on ARM was possible (Mont-Blanc).

- Even though ARM is no longer European, it can form part of the short-term solution

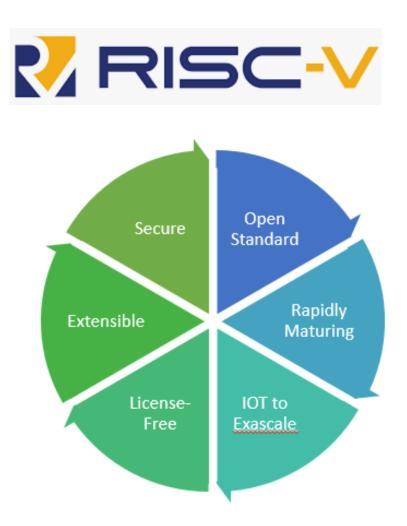

- The fastest-growing movement in computing at the moment is Open-Source and is called RISC-V

- The future is Open and RISC-V is democratising chip-design

# **The Open-Source Hardware Opportunity**

### THE ADVANTAGES....

- RISC-V has no legacy constraints

- RISC-V has (standard and nonstandard) extensions

- RISCV extensions facilitate decoupling from hardware (avoid low level accelerator control, e.g. memory mapped)

- RISC-V is contributed by committees of experts doing a great job

### THE LIMITATIONS....

- Many people's contributions = many different requirements

- Some features may result less important to some members

- The eco-system issue (but smaller than – for example – in consumer market)

- The political issue question

# Special thanks to Mateo Valero Jesus Labarta Eugene Griffiths Fabrizio Gagliardi

# Thank you for attending

Barcelona Supercomputing Center Centro Nacional de Supercomputación