Barcelona Supercomputing Center Centro Nacional de Supercomputación

Pilots and system-level co-design The BSC vision

#### **Prof. Mateo Valero**

**BSC** Director

May 2019, Poznan

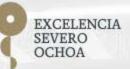

### **The Global Race Towards Exascale**

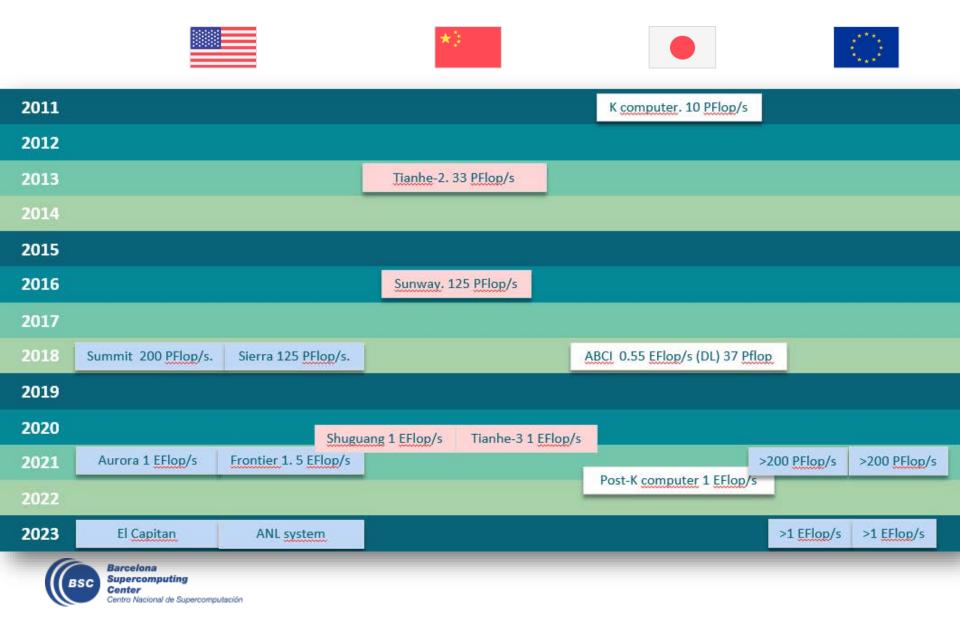

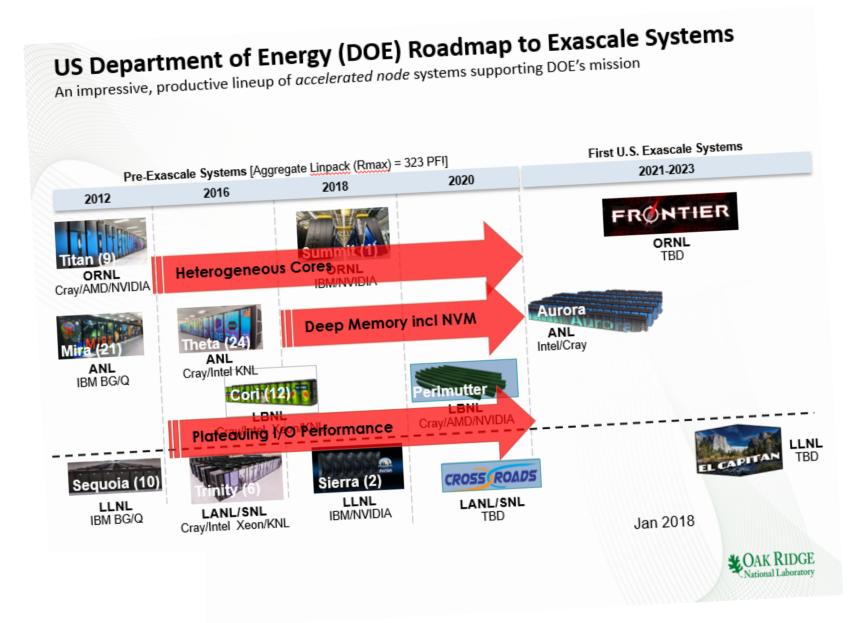

### The Exascale Race – The US example

### **The Exascale Race – The US example**

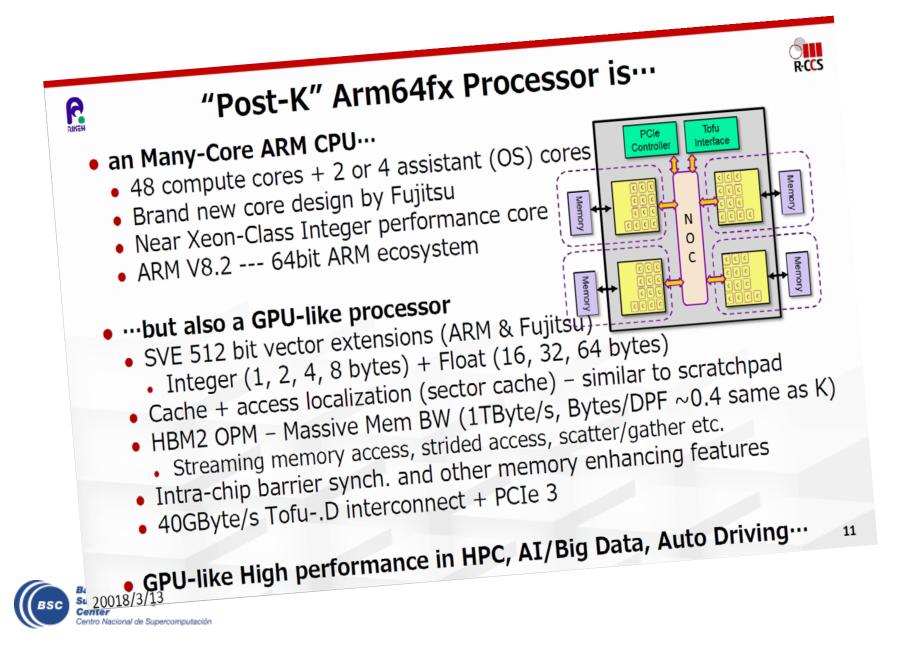

#### The Exascale Race – The Japanese example

#### Co-design from Apps to Architecture

- Architectural Parameters to be determined

- #SIMD, SIMD length, #core, #NUMA node, O3 resources, specialized hardware

- cache (size and bandwidth), memory technologies

- Chip die-size, power consumption

- Interconnect

R

- We have selected a set of target applications

- Performance estimation tool

- Performance projection using Fujitsu FX100 execution profile to a set of arch. parameters.

- Co-design Methodology (at early design phase)

- 1. Setting set of system parameters

- 2. Tuning target applications under the

- system parameters

- 3. Evaluating execution time using prediction

- tools

- 4. Identifying hardware bottlenecks and changing the set of system parameters

Target applications representatives of almost all our applications in terms of computational methods and communication patterns in order to design architectural features.

|   | Target Application |                                                                                                |

|---|--------------------|------------------------------------------------------------------------------------------------|

| ľ | Program            | Brief description                                                                              |

| D | GENESIS            | MD for proteins                                                                                |

| 2 | Genomon            | Genome processing (Genome alignment)                                                           |

| 3 | GAMERA             | Earthquake simulator (FEM in unstructured & structured<br>grid)                                |

| 4 | NICAM+LETK         | Weather prediction system using Big data (structured grid<br>stencil & ensemble Kalman filter) |

| 5 | NTChem             | molecular electronic (structure calculation)                                                   |

| 6 | FFB                | Large Eddy Simulation (unstructured grid)                                                      |

| 2 | RSDFT              | an ab-initio program (density functional theory)                                               |

|   | Adventure          | Computational Mechanics System for Large Scale Analysis<br>and Design (unstructured grid)      |

| C | CCS-QCD            | Lattice QCD simulation (structured grid Monte Carlo)                                           |

#### The Exascale Race – The Japanese example

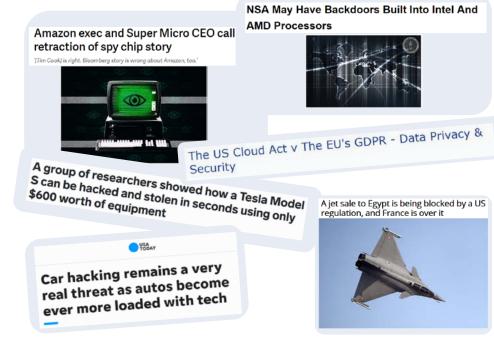

# Why Europe needs its own Processors

- Processors now control almost every aspect of our lives

- Security (back doors etc.)

- Possible future restrictions on exports to EU due to increasing protectionism

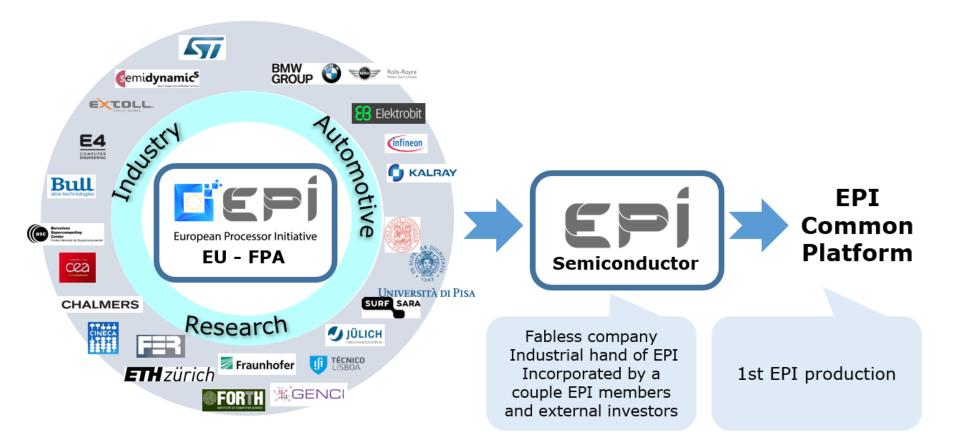

- A competitive EU supply chain for HPC technologies will create jobs and growth in Europe

Images courtesy of European Processor Initiative

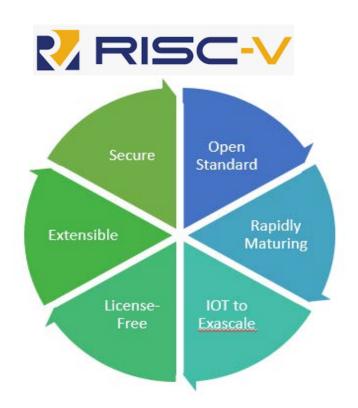

# The Open-Source Hardware Opportunity

- The fastest-growing movement in computing at the moment is Open-Source and is called RISC-V

- The future is open and RISC-V is democratising chip-design

## **EPI. From research to industry**

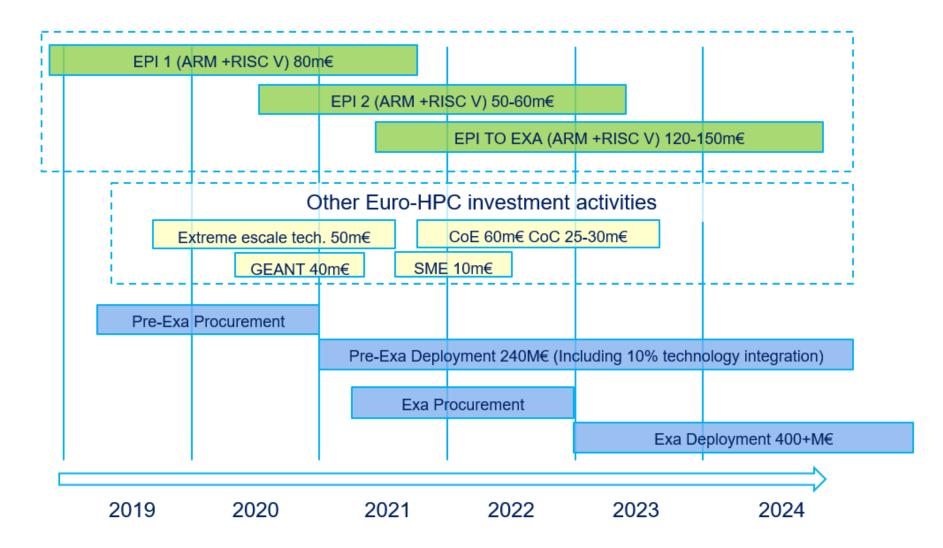

### **The European HPC Roadmap**

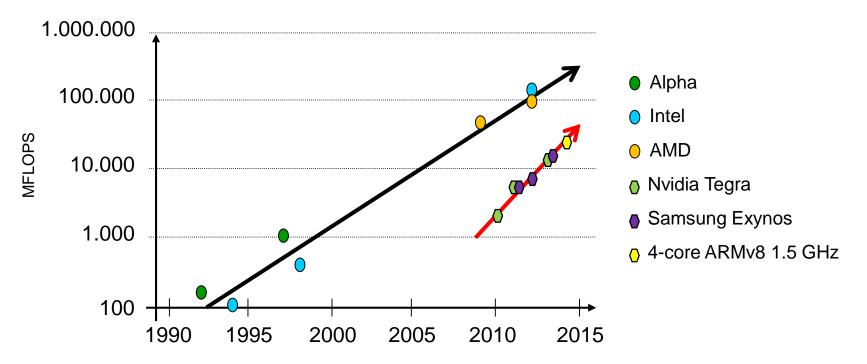

## **The Killer Mobile processors**<sup>™</sup>

- ( Microprocessors killed the Vector supercomputers

- ( They were not faster ...

- ( ... but they were significantly cheaper and greener

- ( History may be about to repeat itself ...

- ( Mobile processor are not faster ...

- Image: Image:

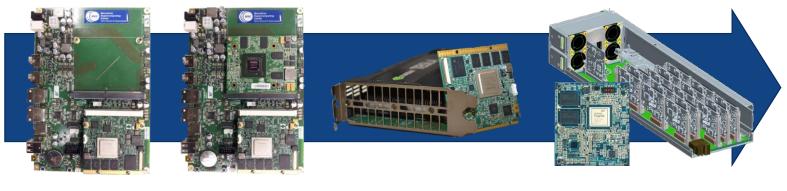

## **Mont-Blanc ARM-based Prototypes**

**2011** Tibidabo **2012** Kayla **2013** Pedraforca

**2014** Mont-Blanc

ARM multicore

ARM + GPU CUDA on ARM ARM + GPU Inifinband RDMA

Single chip ARM+GPU OpenCL on ARM GPU

## The Mont-Blanc HPC Stack for ARM

#### Industrial applications

cional de Supercomputación

Barcelona Supercomputing Center Centro Nacional de Supercomputación

# The EPI Pilot as an Opportunity

- To co-develop an HPC/AI software ecosystem for RISC-V

- Using the hardware coming from EPI (ARM+RISC-V), other EU projects and from any other relevant national and international actors

- Gathering together a wide variety of stakeholders

- BSC would like to collaborate with everyone who can add value

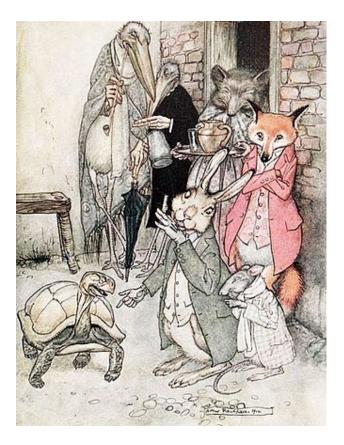

## The Tortoise and the Hare

- Is Aesop's Fable relevant here?

- Are the hares so confident they will win the race, that they are resting?

#### The Tortoise and the Hare

• We are now turbo-charging our tortoise!

#### www.bsc.es

Barcelona Supercomputing Center Centro Nacional de Supercomputación

#### Thank you !!!

For further information please contact mateo.valero@bsc.es